iCE - это торговая марка, используемая для семейства маломощных программируемых вентильных матриц (FPGA), производимых Lattice Semiconductor. Детали этого семейства продаются с лозунгом «самая маленькая в мире ПЛИС» и предназначены для использования в портативных устройствах и устройствах с батарейным питанием (например, мобильных телефонах ), где они будут использоваться для разгрузки задач с главного процессора устройства или системы на чип. При этом главный процессор и его периферийные устройства могут перейти в состояние низкого энергопотребления или полностью отключиться, что потенциально увеличивает срок службы батареи.

Lattice получил бренд iCE в рамках приобретения в 2011 году компании SiliconBlue Technologies.

| | |

| Тип | Частный |

|---|---|

| Промышленность | Интегральные схемы |

| Основан | 12 апреля 2005 г. ( 2005-апрель-12) |

| Учредители | |

| Несуществующий | 9 декабря 2011 г. ( 2011-декабрь-09) |

| Судьба | Приобретена компанией Lattice Semiconductor |

| Штаб-квартира | Санта-Клара, Калифорния, Соединенные Штаты |

| Продукты | ПЛИС |

| Веб-сайт | www.siliconbluetech.com (архивная копия с 2012 г.) |

ПЛИС SiliconBlue ICE65 L

ПЛИС SiliconBlue ICE65 L Ледовая бренд первоначально использовался SiliconBlue Technologies Corporation, бывшим Санта - Клара, Калифорния -А Fabless конструктора интегральных схем. SiliconBlue - это стартап, основанный в 2005 году бывшими сотрудниками Actel, AMD, Lattice, Monolithic Memories и Xilinx. Наиболее известным среди основателей был Джон Биркнер, один из изобретателей логики программируемых массивов.

В 2006 году SiliconBlue финансировался с $ 16 миллионов в «Серии А» капитала, а в июне 2008 года объявила о серии L iCE65 устройств. Устройства должны были быть изготовлены на TSMC «с 65 - нм КМОП - узел процесса, который утверждал SiliconBlue обеспечит снижение расхода энергии по сравнению с современными FPGAs от других производителей. В октябре 2008 года SiliconBlue привлекла еще 24 миллиона долларов в качестве капитала серии B.

В 2009 году потребителям были отгружены первые устройства iCE65 L. SiliconBlue также зарегистрировала SiliconBlue Technologies (Hong Kong) Limited, которая остается дочерней компанией Lattice Semiconductor.

В 2010 году компания SiliconBlue объявила о наименьшем уровне среди устройств iCE65 P. Утверждалось, что устройства на 30% быстрее, чем устройства iCE65 L, при сохранении аналогичного энергопотребления. В июне того же года SiliconBlue закрыла раунд финансирования серии C.

В апреле 2011 года SiliconBlue объявила о выпуске новых семейств продуктов под кодовыми названиями «Лос-Анджелес» и «Сан-Франциско» с использованием технологического узла TSMC 40 нм. Производство устройств на 40- нм техпроцессе было подтверждено в июне 2011 года, когда SiliconBlue получила 18 миллионов долларов в виде финансирования Series D для вывода на рынок устройств с 40- нм технологией. Семейство продуктов iCE40 было официально выпущено в июле 2011 года.

9 декабря 2011 года компания SiliconBlue Technologies была приобретена компанией Lattice Semiconductor путем выкупа наличными за 63,2 миллиона долларов. В рамках этого выкупа Lattice получил бренд iCE, производственные мощности с TSMC и лицензию на различные патенты от Kilopass Technologies, в том числе на технологию одноразовой программируемой памяти XPM (OTP).

В апреле 2012 года Lattice объявила о прекращении производства семейств iCE65. Семейства устройств iCE40 LP и HX начали массовое производство в следующем месяце. Семейство iCE40 LP получило награду Elektra Digital Semiconductor Product of the Year в 2012 году.

В июле 2014 года было анонсировано семейство iCE40 Ultra.

В феврале 2015 года Lattice запустил семейство устройств iCE40 UltraLite. Устройства этого семейства, как утверждается, работают на 30% меньше энергии, чем устройства неуказанных конкурентов, и считаются самыми маленькими в мире ПЛИС, доступными в корпусах 1,4 × 1,4 мм. Семья выиграла награду Elektra Digital Semiconductor Product of the Year 2015.

В декабре 2016 года Lattice запустил семейство устройств iCE40 UltraPlus. Устройства UltraPlus предоставляют дополнительную память, дополнительные элементы обработки и поддержку новых интерфейсов и протоколов по сравнению с предыдущими устройствами iCE40 Ultra / UltraLite.

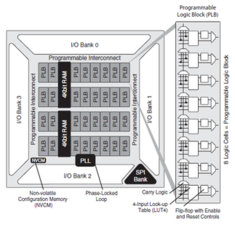

Архитектура устройств iCE40 LP и HX1K. См. Также: ПЛИС § Технический дизайн и ПЛИС § Архитектура.

Архитектура устройств iCE40 LP и HX1K. См. Также: ПЛИС § Технический дизайн и ПЛИС § Архитектура. Устройства iCE65 и iCE40 построены как массив программируемых логических блоков (PLB), где PLB - это блок из восьми логических ячеек. Каждая логическая ячейка состоит из поисковой таблицы с четырьмя входами (иногда называемой 4-LUT или LUT4) с выходом, подключенным к D-триггеру (1- битный элемент хранения). В PLB каждая логическая ячейка соединяется со следующей и предыдущей ячейками с помощью логики переноса, предназначенной для повышения производительности таких конструкций, как сумматоры и вычитатели. С PLB перемежаются блоки RAM, каждый размером четыре килобита. Количество блоков RAM зависит от устройства.

По сравнению с архитектурами на основе LUT6 (такими как устройства серии Xilinx 7 и устройства Altera Stratix ) устройство на основе LUT4 не может реализовывать сложные логические функции с таким же количеством логических ячеек. Например, логическая функция с семью входами может быть реализована в восьми LUT4 или двух LUT6.

Устройства iCE используют энергозависимую SRAM для хранения данных конфигурации. В результате данные должны загружаться в устройство каждый раз при отключении питания. Все устройства iCE поддерживают загрузку данных конфигурации от программатора, с внешней микросхемы флэш-памяти или, за исключением устройств iCE40 LM, из так называемой NVCM или энергонезависимой памяти конфигурации. NVCM - это память с однократным программированием (OTP), интегрированная в FPGA, чтобы исключить необходимость во внешней микросхеме памяти. Решетка утверждает, что использование NVCM может повысить безопасность проектирования, усложняя обратное проектирование.

Эти контакты ввода / вывода на льду устройств разделены на до четырех банков. На некоторых устройствах каждый банк имеет свой собственный вывод питания (обозначенный как V CCIO), позволяющий регулировать высокий логический уровень напряжения банка ввода / вывода. Настраиваемые уровни напряжения ввода-вывода используются устройствами iCE для обеспечения поддержки нескольких стандартов интерфейсов с уровнями напряжения от 1,8 В до 3,3 В, таких как LVDS. Устройства iCE65 также указали, что могут поддерживать SSTL этим методом.

ПЛИС iCE, как и большинство ПЛИС и CPLD, обычно предназначены для использования языка описания оборудования (HDL), который описывает электронную схему. Lattice iCEcube2, IDE, предоставляемая Lattice для разработки на их ПЛИС, поддерживает языки VHDL и Verilog, а также формат EDIF.

Детали формата потока битов конкретной ПЛИС (который определяет, как внутренние элементы ПЛИС связаны и взаимодействуют друг с другом) обычно не публикуются поставщиками ПЛИС. Это означает, что, как правило, инженер, создающий проект для FPGA, должен использовать инструменты, предоставленные производителем FPGA.

В декабре 2015 года на 32C3 Клэр представила инструментарий Project IceStorm, состоящий из инструментов Yosys ( интерфейс синтеза Verilog), Arachne-pnr ( место и маршрут и генерация потока битов) и icepack ( преобразование простого текста в двоичный поток). Вольф, один из двух разработчиков (вместе с Матиасом Лассером) цепочки инструментов. Набор инструментов примечателен тем, что является одним из, если не единственным, набором инструментов с полностью открытым исходным кодом для разработки FPGA. На той же презентации в декабре 2015 года Вольф также продемонстрировал дизайн SoC RISC-V, созданный с использованием набора инструментов с открытым исходным кодом и работающий на устройстве iCE40 HX8K. По состоянию на март 2021 года набор инструментов поддерживает устройства iCE40 LP / HX 1K / 4K / 8K и UP.

Название iCE65 использовалось компанией SiliconBlue Technologies для устройств, разработанных для 65- нм техпроцесса. После приобретения SiliconBlue в 2011 году это имя использовалось Lattice Semiconductor, пока семейство не было прекращено в апреле 2012 года.

| Ряд | Устройство | LE | баран | ФАПЧ | Максимум. Ввод / вывод |

|---|---|---|---|---|---|

| iCE65 L | L01 | 1280 | 64 кбит | N / A | 95 |

| L04 | 3520 | 80 кбит | 176 | ||

| L08 | 7680 | 128 кбит | 222 | ||

| L16 | 16 896 | 384 кбит | Неизвестный | ||

| iCE65 P | P04 | 3520 | 80 кбит | 1 | 174 |

| P08 | 7680 | 128 кбит | 2 | Неизвестный | |

| P12 | 12 160 | 160 кбит | 2 | Неизвестный |

L iCE65 серия устройств была предназначена для маломощных приложений и портативных устройств. Впервые о серии было объявлено в середине 2008 года, а массовым покупателям она была отправлена в начале 2009 года.

Информация о более крупном устройстве в этой серии, iCE65L16, была указана на веб-сайте SiliconBlue в 2010 году, но не упоминается в версии 2012 года спецификации L-серии. Неясно, производилось ли когда-либо устройство серийно.

Устройства серии iCE65 P продавались как высокопроизводительная версия устройств серии L, предназначенная для использования в дисплеях, памяти и приложениях SERDES, и были анонсированы в начале 2010 года. Три устройства были перечислены как часть серии но только одно устройство, iCE65P04 самого низкого уровня, было полностью определено. В последнем техническом описании семейства, опубликованном в 2011 году, перечислены две другие части, но не даны спецификации. Неясно, производились ли когда-либо эти два других устройства серийно.

Lattice использует название iCE40 для своих устройств под брендом iCE, производимых на технологическом узле 40 нм. Компания также использовала кодовое название «Лос-Анджелес» в пресс-релизах. Семейство iCE40 было запущено в июле 2011 года с деталями iCE40 LP и HX и было обновлено в июле 2014 года деталями iCE40 Ultra, в феврале 2015 года деталями iCE40 UltraLite и в декабре 2016 года деталями iCE40 UltraPlus.

| Семья | Устройство | LE | баран | I²C | SPI | DSP | ШИМ | Максимум. Ввод / вывод |

|---|---|---|---|---|---|---|---|---|

| UltraLite | UL640 | 640 | 56 кбит | 2 | N / A | | 26 год | |

| UL1K | 1280 | 56 кбит | 2 | | 26 год | |||

| Ультра | iCE5LP1K | 1100 | 64 кбит | 1 | 1 | 2 | | 39 |

| iCE5LP2K | 2048 | 80 кбит | 2 | 2 | 4 | | 39 | |

| iCE5LP4K | 3520 | 80 кбит | 2 | 2 | 4 | | 39 | |

| UltraPlus | UP3K | 2800 | 1104 кбит | 2 | 2 | 4 | | 21 год |

| UP5K | 5280 | 1144 кбит | 2 | 2 | 8 | | 39 | |

Устройства iCE40 Ultra, UltraLite и UltraPlus предназначены для приложений с особенно низкими ограничениями доступного пространства и мощности, таких как носимые устройства и умные часы. Они предлагаются в корпусах в масштабе микросхемы, BGA и QFN с размерами от 1,4 × 1,4 мм до 7 × 7 мм. Все устройства в семействе объединяют одно или два жестких ядра I²C, а устройства Ultra и UltraPlus также включают ядра жесткой шины SPI и блоки DSP. Утверждается, что устройства UltraLite работают при половинном потреблении статического тока устройств Ultra (35 мкА по сравнению с 71 мкА). Большинство устройств этого семейства также включают в себя ШИМ- контроллер, предназначенный для управления светодиодами IR или RGB.

Компания Lattice выпустила семейство Ultra в середине 2014 года, а семейство UltraLite - в начале 2015 года. В 2015 году семейство UltraLite было удостоено награды Elektra Digital Semiconductor Product of the Year.

В сентябре 2016 года был выпущен Apple iPhone 7, в котором использовалось устройство iCE5LP4K.

В декабре 2016 года Lattice запустил семейство UltraPlus, предназначенное для распределенной обработки и так называемых «мобильных гетерогенных вычислений ». Эти устройства включают в себя 1 Мбит (4 × 256 кбит) с одним портом ОЗУ (сравните с двухпортовой RAM ), дополнительные элементы обработки DSP, а также поддержка дополнительных интерфейсов, таких как MIPI I3C, D-PHY и Virtual GPIO.

| Семья | Устройство | LE | баран | I²C | SPI | ФАПЧ | Максимум. Ввод / вывод |

|---|---|---|---|---|---|---|---|

| LP | LP384 | 384 | | N / A | | 39 | |

| LP640 | 640 | 32 кбит | | 11 | |||

| LP1K | 1280 | 64 кбит | 1 | 97 | |||

| LP4K | 3520 | 80 кбит | 2 | 180 | |||

| LP8K | 7680 | 128 кбит | 2 | 180 | |||

| LM | LM1K | 1100 | 64 кбит | 2 | 2 | 1 | 39 |

| LM2K | 2048 | 80 кбит | 2 | 2 | 1 | 39 | |

| LM4K | 3520 | 80 кбит | 2 | 2 | 1 | 39 | |

Компоненты iCE40 LP (с низким энергопотреблением) и LM (с низким энергопотреблением с жестким IP ) предназначены для использования в устройствах с батарейным питанием в качестве аппаратных ускорителей и расширителей портов ввода-вывода, а также для использования в тех же приложениях, что и компоненты iCE40 Ultra и UltraLite. По сравнению с деталями Ultra детали LP и LM доступны в более широком диапазоне посадочных мест, предлагают большее количество ресурсов (выводы ввода-вывода, встроенная оперативная память и логические элементы), но потребляют больше энергии.

Устройства LP отличаются от устройств Ultra тем, что в них нет жестких IP-ядер. Вместо этого любая логика интерфейса должна быть реализована в матрице FPGA. Как правило, это менее предпочтительно, поскольку так называемые «мягкие ядра» менее энергоэффективны, чем жесткие ядра, и часто не могут работать на тех же частотах. Мягкое ядро также уменьшает количество логических ячеек, доступных приложению. Устройства LM объединяют два жестких ядра I²C и два SPI, а также два генератора стробов. Большинство устройств LP и LM имеют один или два контура фазовой автоподстройки частоты.

Семейства были запущены в производство в середине 2011 года и начали массовое производство в середине 2012 года. Они выиграли награду Elektra Digital Semiconductor Product of the Year в 2012 году. В 2015 году было объявлено, что ZTE будет использовать устройства LM для обеспечения функций концентратора датчиков и инфракрасного пульта дистанционного управления. в своем смартфоне Star 2.

| Устройство | LE | баран | ФАПЧ | Статический ток | Максимум. Ввод / вывод |

|---|---|---|---|---|---|

| HX1K | 1280 | 64 кбит | 1 | 296 мкА | 98 |

| HX4K | 3520 | 80 кбит | 2 | 1140 мкА | 109 |

| HX8K | 7680 | 128 кбит | 2 | 1140 мкА | 208 |

Устройства iCE40 HX предназначены для высокопроизводительных приложений. По сравнению с устройствами iCE40 LP и Ultra, они предлагают более низкую максимальную задержку распространения (7,30 нс против 9,00–9,36 нс) и больше контактов ввода / вывода. Устройства серии HX потребляют значительно больше статической энергии и доступны только в значительно большей занимаемой площади по сравнению с деталями Ultra и LP (от 7 × 7 мм до 2 × 2 см). Подобно устройствам LP, части HX не имеют жестких IP-ядер, но обеспечивают один или два контура фазовой автоподстройки частоты. В отличие от других устройств iCE40, детали HX также доступны в посадочных местах QFP.

В HX части были начаты в середине 2011 года вместе с LP частей и вступили объем производство в середине 2012 года.