Схема из оригинального патента Видлара

Схема из оригинального патента Видлара A Источник тока Видлара является модификацией основные два- транзистора токовое зеркало, которое включает в себя резистор вырождения эмиттера только для выходного транзистора, что позволяет источнику тока генерировать низкие токи с использованием резисторов только умеренных значений.

Схема Видлара может использоваться с биполярными транзисторами, МОП-транзисторами и даже электронными лампами. Примером применения является операционный усилитель 741, и Видлар использовал эту схему в составе многих своих проектов.

Эта схема названа в честь ее изобретателя, Боба Видлара, и был запатентован в 1967 году.

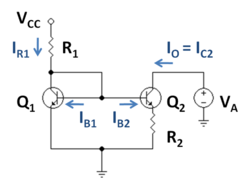

Рисунок 1: Вариант источника тока Видлара с использованием биполярных транзисторов.

Рисунок 1: Вариант источника тока Видлара с использованием биполярных транзисторов. Рисунок 1 является пример источника тока Видлара, использующий биполярные транзисторы, в котором эмиттерный резистор R 2 подключен к выходному транзистору Q 2 и имеет эффект уменьшения тока в Q 2 относительно Q 1. Ключ к этой схеме состоит в том, что падение напряжения на резисторе R 2 вычитается из напряжения база-эмиттер транзистора Q 2, тем самым отключая этот транзистор по сравнению с транзистором Q <75.>1. Это наблюдение выражается приравниванием выражений базового напряжения, найденных с обеих сторон цепи на рисунке 1, как:

, где β 2 - бета-значение выходного транзистора, которое не совпадает с бета-значением входного транзистора в отчасти потому, что токи в двух транзисторах очень разные. Переменная I B2 - это базовый ток выходного транзистора, V BE - это напряжение база-эмиттер. Это уравнение подразумевает (используя закон диодов Шокли ):

Eq. 1

![{\ displaystyle {\ begin {align} (\ beta _ {2} +1) I_ {B2} = \ left (1 + {\ frac {1} {\ beta _ {2}}} \ right) I_ {C2} = {\ frac {1} {R_ {2}}} \ left (V_ {BE1} -V_ {BE2} \ right) \\ = {\ frac {V _ {\ text {T}}} {R_ {2}}} \ left [\ ln \ left (I_ {C1} / I_ {S1} \ right) - \ ln \ left (I_ { C2} / I_ {S2} \ right) \ right] = {\ frac {V _ {\ text {T}}} {R_ {2}}} \ ln \ left ({\ frac {I_ {C1} I_ {S2 }} {I_ {C2} I_ {S1}}} \ right) \, \ end {выравнивается}}}](https://wikimedia.org/api/rest_v1/media/math/render/svg/2fe36a235ecb9c1bd0e3eedd49a6363f645cfeca)

где V T - тепловое напряжение.

Это уравнение делает приближение того, что оба тока намного больше, чем масштабные токи, I S1 и I S2 ; приближение действительно, за исключением текущих уровней около отсечки. В дальнейшем предполагается, что токи шкалы идентичны; на практике это нужно специально организовывать.

Для проектирования зеркала выходной ток должен быть связан с двумя значениями резистора R 1 и R 2. Основное наблюдение состоит в том, что выходной транзистор находится в активном режиме только до тех пор, пока его напряжение коллектор-база не равно нулю. Таким образом, простейшее условие смещения для конструкции зеркала устанавливает приложенное напряжение V A равным базовому напряжению V B. Это минимальное полезное значение V A называется согласованным напряжением источника тока. При таком условии смещения ранний эффект не играет роли в конструкции.

Эти соображения предполагают следующую процедуру проектирования:

Обратная задача проектной задачи определяет ток, когда известны значения резистора. Далее описывается итерационный метод. Предположим, что источник тока смещен, поэтому напряжение коллектор-база выходного транзистора Q 2 равно нулю. Ток через R 1 - это входной или опорный ток, заданный как,

Переупорядочивание, I C1 находится как:

Eq. 2

Уравнение диода дает:

Ур. 3

Уравнение 1 обеспечивает:

Эти три отношения являются нелинейным, неявным определением токов, которые могут быть решены с помощью итераций.

Эта процедура повторяется до сходимости и удобно настраивается в электронной таблице. Можно просто использовать макрос для копирования новых значений в ячейки электронной таблицы, содержащие начальные значения, чтобы получить решение в короткие сроки.

Обратите внимание, что при показанной схеме, если V CC изменяется, выходной ток изменится. Следовательно, чтобы поддерживать постоянный выходной ток, несмотря на колебания V CC, цепь должна управляться источником постоянного тока , а не резистором R 1.

Приведенные выше трансцендентные уравнения могут быть решены точно в терминах W-функции Ламберта.

Рисунок 2: Схема слабого сигнала для определения выходного сопротивления источника Видлара показано на рисунке 1. На выходе подается испытательный ток I x, и выходное сопротивление тогда R O = V x / I x.

Рисунок 2: Схема слабого сигнала для определения выходного сопротивления источника Видлара показано на рисунке 1. На выходе подается испытательный ток I x, и выходное сопротивление тогда R O = V x / I x.Важным свойством источника тока является его инкрементный выходной импеданс небольшого сигнала, который в идеале должен быть бесконечным. Схема Видлара обеспечивает локальную обратную связь по току для транзистора

Выходное сопротивление определяется с использованием модели слабого сигнала для схемы, показанной на рисунке 2. Транзистор Q 1 заменяется его эмиттерным сопротивлением слабого сигнала r E Потому что это диодно подключено. Транзистор Q 2 заменяется его гибридной пи-моделью. На выходе подается испытательный ток I x.

Используя рисунок, выходное сопротивление определяется по законам Кирхгофа. Используя закон напряжения Кирхгофа от земли слева к заземлению соединения R 2:

![I_ {b} \ left [(R_ {1} \ parallel r_ {E}) + r _ {\ pi} \ right] + [I_ {x} + I_ {b}] R_ {2} = 0 \.](https://wikimedia.org/api/rest_v1/media/math/render/svg/3862be56e5a63578fd1bf57900a13aedaa94788c)

Изменение порядка:

Используя закон Кирхгофа относительно заземления R 2 на землю испытательного тока:

или, заменив I b:

Eq. 4

![R_ {O} = {\ frac {V_ {x}} {I_ {x}}} = r_ {O} \ left [1 + {\ frac {\ beta R_ {2}} {(R_ {1} \ параллельно r_ {E}) + r _ {\ pi} + R_ {2 }}} \ right]](https://wikimedia.org/api/rest_v1/media/math/render/svg/d8b1cfc4fd11db5b1b3d090da8cfbd0e592e0095)

![+ \ R_ {2} \ left [{\ frac { (R_ {1} \ parallel r_ {E}) + r _ {\ pi}} {(R_ {1} \ parallel r_ {E}) + r _ {\ pi} + R_ {2}}} \ right] \.](https://wikimedia.org/api/rest_v1/media/math/render/svg/033a7d64c94712c0e8c1e3cf1bfcd747be5318e7)

Согласно уравнению. 4, выходное сопротивление источника тока Видлара увеличивается по сравнению с выходным сопротивлением самого выходного транзистора (которое составляет r O), пока R 2 достаточно велико по сравнению с r π выходного транзистора (большие сопротивления R 2 заставляют множитель r O приближаться к значению (β + 1)). Выходной транзистор несет низкий ток, что делает r π большим, и увеличение R 2 имеет тенденцию к дальнейшему уменьшению этого тока, вызывая коррелированное увеличение r π. Следовательно, цель R 2 r π может быть нереалистичной, и дальнейшее обсуждение предоставляется ниже. Сопротивление R 1∥rEобычно невелико, поскольку сопротивление эмиттера r E обычно составляет всего несколько Ом.

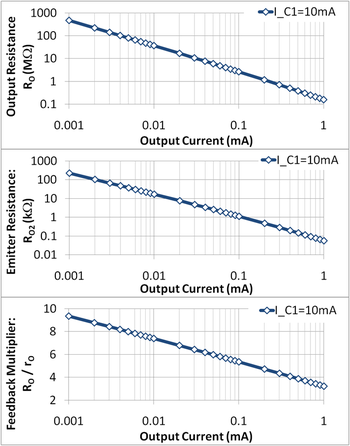

Рис. 3. Расчетный компромисс между выходным сопротивлением и выходным током. Верхняя панель: Выходное сопротивление цепи R O vs. Выходной ток постоянного тока I C2 с использованием расчетной формулы Ур. 5 для R 2; Центральная панель: сопротивление R O2 в эмиттерной ветви выходного транзистора; Нижняя панель: Коэффициент обратной связи, влияющий на выходное сопротивление. Ток в опорном транзисторе Q 1 удерживается постоянная, тем самым фиксируя напряжение соответствия. Графики предполагают, что I C1 = 10 мА, V A = 50 В, V CC = 5 В, I S = 10 фА, β 1, 2 = 100 независимо от тока.

Рис. 3. Расчетный компромисс между выходным сопротивлением и выходным током. Верхняя панель: Выходное сопротивление цепи R O vs. Выходной ток постоянного тока I C2 с использованием расчетной формулы Ур. 5 для R 2; Центральная панель: сопротивление R O2 в эмиттерной ветви выходного транзистора; Нижняя панель: Коэффициент обратной связи, влияющий на выходное сопротивление. Ток в опорном транзисторе Q 1 удерживается постоянная, тем самым фиксируя напряжение соответствия. Графики предполагают, что I C1 = 10 мА, V A = 50 В, V CC = 5 В, I S = 10 фА, β 1, 2 = 100 независимо от тока. Токовая зависимость сопротивлений r π и r O обсуждается в статье гибрид-пи модель. Текущая зависимость номиналов резисторов:

и

- выходное сопротивление из-за раннего эффекта, когда V CB = 0 В (параметр устройства V A - раннее напряжение).

Из ранее в этой статье (устанавливая равные токи шкалы для удобства): Ур. 5

Следовательно, для обычного случая малого r E и пренебрегая второй член в R O с ожиданием, что главный член, включающий r O, намного больше: уравнение. 6

, где последняя форма находится заменой Ур. 5 для R 2. Ур. 6 показывает, что значение выходного сопротивления, намного превышающее r O выходного транзистора, получается только для схем с I C1>>I C2. На рисунке 3 показано, что выходное сопротивление схемы R O определяется не столько обратной связью, сколько текущей зависимостью сопротивления r O выходного транзистора (выходное сопротивление на рисунке 3 изменяется на четыре порядка, а коэффициент обратной связи - только на один порядок).

Увеличение I C1 для увеличения коэффициента обратной связи также приводит к увеличению податливого напряжения, что не очень хорошо, поскольку это означает, что источник тока работает в более ограниченном диапазоне напряжений. Так, например, с целью установить соответствие напряжения, установив верхний предел на I C1, и с целью достижения выходного сопротивления максимальное значение выходного тока I C2 ограничено.

Центральная панель на Рисунке 3 показывает компромисс между сопротивлением эмиттерной ветви и выходным током: меньший выходной ток требует большего резистора ветви и, следовательно, большей площади для конструкции. Таким образом, верхняя граница площади устанавливает нижнюю границу выходного тока и верхнюю границу выходного сопротивления схемы.

Ур. 6 для R O зависит от выбора значения R 2 в соответствии с уравнением. 5. Это означает, что уравнение. 6 - это не формула поведения схемы, а уравнение расчетной стоимости. Как только R 2 выбран для конкретной цели проектирования с использованием Ур. 5, после этого его значение фиксируется. Если работа схемы вызывает отклонение токов, напряжений или температур от расчетных значений; затем для прогнозирования изменений в R O, вызванных такими отклонениями, Ур. 4 следует использовать, а не уравнение. 6.