Вспышка ловушки заряда (CTF ) - это технология полупроводниковой памяти используется при создании энергонезависимой NOR и NAND флэш-памяти. Это тип MOSFET с плавающим затвором технологии памяти, но отличается от традиционной технологии с плавающим затвором тем, что в нем для хранения электронов используется пленка нитрида кремния. вместо легированного поликристаллического кремния, типичного для структуры с плавающим затвором. Такой подход позволяет производителям памяти сократить производственные затраты пятью способами:

Концепция улавливания заряда была впервые представлена Тингом Л. Чу в 1967 году, и только в 2002 году AMD и Fujitsu производили флэш-память большого объема с улавливанием заряда. Они начали коммерческое производство флэш-памяти с улавливанием заряда, представив семейство флэш-памяти GL NOR. Тот же самый бизнес, ныне работающий под названием Spansion, с тех пор в больших количествах производит устройства для улавливания заряда. Флэш-память для улавливания заряда составила в 2008 году 30% рынка флэш-памяти NOR стоимостью 2,5 миллиарда долларов. Saifun Semiconductors, которая лицензировала большой портфель технологий улавливания заряда нескольким компаниям, была приобретена Spansion в марте 2008 года. С конца 2000-х годов CTF стала основным компонентом 3D V-NAND флэш-память, разработанная Toshiba и Samsung Electronics.

Исходный MOSFET (полевой транзистор металл-оксид-полупроводник, или МОП-транзистор) был изобретен египетским инженером Мохамедом М. Аталлой и корейским инженером Давоном Кангом в Bell Labs в 1959 году и продемонстрирован в 1960 году. изобрести MOSFET с Саймоном Мин Сзе в Bell Labs, и они предложили использовать его в качестве памяти с плавающим затвором (FG) ячейка, в 1967 году. Это была первая форма энергонезависимой памяти, основанная на введении и хранении зарядов в полевом МОП-транзисторе с плавающим затвором, который позже стал основой для EPROM (стираемый PROM ), EEPROM (электрически стираемый PROM) и флэш-память.

В конце 1967 года исследовательская группа Сперри под руководством Х.А. Ричард Вегенер, А.Дж. Линкольн и Х. Пао изобрел транзистор металл-нитрид-оксид-полупроводник (MNOS-транзистор), тип полевого МОП-транзистора, в котором слой оксида заменен двойным слоем из нитрида <86.>и оксид. Нитрид использовался в качестве улавливающего слоя вместо плавающего затвора, но его использование было ограничено, поскольку считалось, что он уступает плавающему затвору. Устройство MNOS-транзистора может быть запрограммировано путем приложения 50-вольтного прямого или обратного смещения между затвором и каналом для улавливания зарядов, которые могут повлиять на пороговое напряжение транзистора.

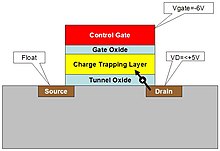

Зарядная ловушка (CT) была представлена в устройствах MNOS в конце 1960-х годов. Он имел структуру устройства и принципы работы, аналогичные памяти с плавающим затвором (FG), но основное отличие состоит в том, что заряды хранятся в проводящем материале (обычно в слое FG из легированного поликремния ), тогда как В памяти CT хранятся заряды в локализованных ловушках внутри диэлектрического слоя (обычно сделанного из нитрида кремния ).

К 1974 году технология улавливания заряда использовалась в качестве механизма хранения в электрически стираемой программируемой постоянной памяти (EEPROM) и являлась альтернативой стандартной технологии MOSFET с плавающим затвором. В 1977 году PCY Chen из Fairchild Camera and Instrument опубликовал документ, в котором подробно описывается изобретение SONOS, технологии MOSFET с гораздо менее требовательными программами и условиями стирания и более длительным хранением заряда. Это улучшение привело к созданию производимых устройств EEPROM на основе заряда - улавливание SONOS в 1980-х.

В 1991 году японцы Исследователи NEC, в том числе Н. Кодама, К. Ояма и Хироки Сираи, разработали тип флэш-памяти, включающий метод улавливания заряда. В 1998 году израильский инженер Боаз Эйтан из Saifun Semiconductors (позже приобретенный Spansion ) запатентовал технологию флэш-памяти под названием NROM, которая использовала преимущества слоя улавливания заряда для замены плавающего затвора, используемого в традиционных конструкциях флэш-памяти. В этом патенте появляются два важных нововведения: локализация инжектированных отрицательных и положительных зарядов рядом с выводами стока / истока элемента и использование концепции обратного чтения для обнаружения сохраненных данных элемента на обоих концах ловушки для заряда. Эти две новые идеи сделали возможным высокую цикличность, тем самым позволив производить надежные импульсные устройства с улавливанием заряда, впервые с момента изобретения концепции улавливания заряда 30 лет назад. Кроме того, используя эти концепции, можно создать два отдельных физических бита на ячейку, удваивая емкость хранимых данных на ячейку.

В 2000 году исследовательская группа Advanced Micro Devices (AMD) под руководством Ричарда М. Фастоу, египетского инженера Халеда З. Ахмеда и иорданского инженера Самира Хаддада (который позже присоединился к Spansion) продемонстрировала механизм улавливания заряда для NOR flash ячеек памяти. Эти нововведения были дополнительно усовершенствованы в AMD и Fujitsu в 2002 году (а затем и в Spansion), и впервые эти компании начали массовое производство в так называемой «флэш-памяти MirrorBit».

Флэш-память с захватом заряда (CTF) была коммерциализирована AMD и Fujitsu в 2002 году. В том же году AMD (в подразделение позже было выделено как Spansion) объявила о новой технологии флэш-памяти под названием MirrorBit. Компания Spansion использовала этот продукт для снижения производственных затрат и расширения диапазона плотности флэш-памяти NOR по сравнению с обычной флэш-памятью NOR, а также для соответствия стоимости многоуровневой ячейки флэш-памяти NOR, производимой Intel.

Spansion MirrorBit Cell

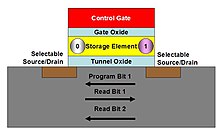

Spansion MirrorBit Cell В ячейке MirrorBit используется слой улавливания заряда не только как замена обычного плавающего затвора, но и из-за непроводящего характера нитрида накопления заряда, позволяющего двум битам совместно использовать та же ячейка памяти. Как показано на рисунке 1, биты находятся на противоположных концах ячейки и могут быть прочитаны путем пропускания тока через канал в разных направлениях.

Были успешно созданы продукты, сочетающие этот подход с технологией многоуровневых ячеек, чтобы содержать четыре бита в ячейке.

Подобно ячейке памяти с плавающим затвором, Ячейка улавливания заряда использует переменный заряд между управляющим затвором и каналом для изменения порогового напряжения транзистора. Механизмы изменения этого заряда относительно похожи между плавающим затвором и ловушкой заряда, и механизмы считывания также очень похожи.

Во вспышке с захватом заряда электроны сохраняются в улавливающем слое точно так же, как они хранятся в плавающем затворе в стандартной флэш-памяти, EEPROM или СППЗУ. Ключевое отличие состоит в том, что слой, улавливающий заряд, является изолятором, а плавающий затвор - проводником.

Высокие нагрузки записи во флеш-память вызывают напряжение в туннельном оксидном слое, создавая небольшие нарушения в кристаллической решетке, называемые «оксидными дефектами». Если возникает большое количество таких сбоев, возникает короткое замыкание между плавающим затвором и каналом транзистора, и плавающий затвор больше не может удерживать заряд. Это основная причина износа флеш-памяти (см. Флэш-память # Износ памяти ), которая определяется как «выносливость» микросхемы. Чтобы уменьшить возникновение таких коротких замыканий, вспышка с плавающим затвором изготавливается из толстого туннельного оксида (~ 100 Å), но это замедляет стирание при использовании туннелирования Фаулера-Нордхейма и вынуждает конструкцию использовать более высокое туннельное напряжение, которое ложится новой нагрузкой на другие части микросхемы.

Ячейка улавливания заряда относительно невосприимчива к таким трудностям, поскольку слой улавливания заряда является изолятором. Короткое замыкание, вызванное оксидным дефектом между слоем улавливания заряда и каналом, будет истощать только электроны, находящиеся в непосредственном контакте с коротким замыканием, оставляя другие электроны на месте, чтобы продолжать контролировать пороговое напряжение транзистора. Поскольку короткие замыкания вызывают меньшую озабоченность, можно использовать более тонкий туннельный оксидный слой (50-70 Å), увеличивающий сцепление улавливающего слоя с каналом и приводящий к более высокой скорости программы (с локализованными захваченными зарядами) и стиранию с более низкими туннельными напряжениями. Более низкие туннельные напряжения, в свою очередь, создают меньшую нагрузку на туннельный оксидный слой, что приводит к меньшему количеству разрушений решетки.

Еще одно важное преимущество использования ячейки улавливания заряда заключается в том, что тонкий слой улавливания заряда снижает емкостную связь между соседними ячейками, чтобы улучшить производительность и масштабируемость.

Электроны перемещаются на слой, улавливающий заряд, аналогично тому, как программируется ИЛИ-вспышка с плавающим затвором, через механизм инжекции горячих электронов (CHE), также известный как инжекция горячих носителей. Короче говоря, высокое напряжение помещается между управляющим затвором, в то время как среднее или высокое напряжение прикладывается к истоку и стоку, в то время как ток индуцируется от истока к стоку. Те электроны, которые набрали достаточную энергию при прохождении через область сильного поля рядом со стоком, будут выкипать из канала и инжектироваться в слой улавливания заряда, где они останавливаются.

Вспышка захвата заряда стирается посредством инжекции горячих дырок (см. инжекция горячих носителей ), в отличие от туннелирования Фаулера-Нордхейма подход, используемый как для NAND, так и для NOR flash для стирания. В этом процессе используется поле, а не ток, используемый в FN, для перемещения дыр к слою, улавливающему заряд, для удаления заряда.

Производство вспышки для захвата заряда аналогично производству с плавающим затвором с некоторыми исключениями, которые служат для упрощения производства.

И вспышка с плавающим затвором, и вспышка с захватом заряда используют многослойную структуру затвора, в которой плавающий затвор или слой улавливания заряда находится непосредственно над каналом и ниже управляющего затвора.. Плавающий затвор или слой улавливания заряда изолирован от канала туннельным оксидным слоем и от управляющего затвора оксидным слоем затвора. Материалы для всех этих слоев одинаковы, за исключением накопительного слоя, который представляет собой проводящий поликремний для структуры с плавающим затвором и обычно представляет собой нитрид кремния для ловушки заряда.

Freescale Semiconductor производит в чем-то похожую технологию, которую компания называет «Thin Film Storage» в своих микроконтроллерах или линейке MCU. Подход Freescale использует кремниевые нанокристаллы в качестве проводящих островков в непроводящем слое оксида кремния.

Как и более обычная ловушка заряда из нитрида кремния, электроны не перетекают с одной стороны плавающего затвора на другую, увеличивая износ элемента.

Этот подход на основе нанокристаллов в больших объемах производится Freescale, а накопители с улавливанием заряда в целом разрабатываются в ST Microelectronics, Philips, Renesas, Samsung, Toshiba, Atmel и Spansion.

Поскольку слой, улавливающий заряд нитрида, не является проводящим, его не нужно создавать - все улавливатели заряда уже изолированы друг от друга. Это можно использовать для упрощения производства.

Структуры с плавающим затвором требовали более сложных диэлектриков затвора в течение нескольких последних поколений процессов, и сегодня обычно используется структура ONO (оксид-нитрид-оксид), которая более сложна в изготовлении и не нужна во вспышках с захватом заряда..

Одним из преимуществ нитридного слоя является то, что он менее чувствителен к высокотемпературной производственной обработке, чем поликремний, используемый в плавающем затворе. Это упрощает обработку слоев над зарядовой ловушкой.

В маркетинговой брошюре Spansion заявила, что стоимость обработки флеш-пластины MirrorBit NOR ниже, чем у обычной пластины с плавающим затвором, поскольку на 10% меньше шагов маски фотолитографии и на 40% меньше «критических» шагов (требующих высочайшего разрешения и, следовательно, самого дорогого фотолитографического оборудования). Маркетинговые материалы Infineon показали, что для изготовления флэш-памяти NAND с улавливанием заряда требуется на 15% меньше шагов маски, чем для производства эквивалентного продукта с плавающим затвором.

MirrorBit Flash от Spansion и NROM от Saifun - это две флэш-памяти, в которых используется механизм улавливания заряда в нитриде для хранения двух битов в одной и той же ячейке, эффективно удваивая емкость памяти микросхемы. Это достигается размещением зарядов по обе стороны от слоя ловушки заряда. Ячейка считывается с использованием прямого и обратного токов через канал для считывания с любой стороны зарядовой ловушки.

Рисунок 2. Программирование добавляет электроны в ловушку заряда посредством инжекции горячих электронов

Рисунок 2. Программирование добавляет электроны в ловушку заряда посредством инжекции горячих электронов Во время программирования CHE (Рисунок 2) горячие электроны инжектируются из канала в слой улавливания заряда в направлении смещенного конца стока канала, но не со стороны плавающего истока канала. Позволяя истоку и стоку транзистора переключаться с одного конца канала на другой, заряды могут вводиться и сохраняться в слое улавливания заряда на любом конце канала.

Рис. 3. Стирание удаляет электроны из ловушки заряда посредством инжекции горячих дырок.

Рис. 3. Стирание удаляет электроны из ловушки заряда посредством инжекции горячих дырок. Аналогичным образом, один конец ячейки улавливания заряда можно стереть, поместив стирающее поле на один или другой конец канала, позволяя другому концу "плавать", как показано на рисунке 3. Межзонное стирание горячих дырок создает локально захваченные дыры, некоторые из которых рекомбинируют с электронами, чтобы удалить заряд с этого конца зарядовой ловушки.

Чтение MirrorBit выполняется очень просто путем переключения контактов истока и стока. Область истощения перехода, проходящая со стороны стока, экранирует канал от заряда на стороне ячейки улавливания заряда, которая перекрывает сток. Конечным результатом этого является то, что заряд на стороне стока мало влияет на ток, протекающий через канал, в то время как заряд на стороне истока определяет порог транзистора.

Когда исток и сток меняются местами, заряд противоположной стороны определяет порог транзистора.

Таким образом, два разных уровня заряда на обоих концах ячейки улавливания заряда вызовут два разных тока, протекающих через ячейку, в зависимости от направления тока.

Samsung Electronics в 2006 году раскрыли свое исследование использования флэш-памяти с улавливанием заряда, чтобы обеспечить дальнейшее масштабирование технологии NAND с использованием ячейки структуры, похожие на плоские конструкции, использовавшиеся в то время. Технология зависит от структуры конденсатора SONOS (кремний – оксид – нитрид – оксид – кремний) или MONOS (металл – ONOS), хранящей информацию в ловушках заряда в слое нитрида.

Samsung раскрыла две структуры ячеек: TANOS (титан, оксид алюминия, нитрид, оксид, кремний) для 40 нм, при этом исследователи полагали, что существующая трехмерная структура крышки (подробно описанная ниже в этой статье) не может быть изготовлена, и THNOS, в котором оксид алюминия будет заменен нераскрытым материалом с высоким k-диэлектриком. Ожидалось, что материал с высоким k даст более длительное время удерживания, чем структура оксида алюминия.

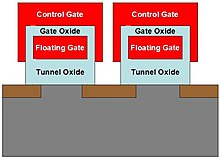

В конструкции крышки управляющий затвор расширяется для образования барьера между соседними плавающими затворами в обычной ячейке с плавающим затвором.

В течение следующих пяти лет многие разработчики устройств нашли способы подтолкнуть структуру крышки к все более жесткой геометрии процесса, успешно создавая NAND в узле 30 нм с этим подходом.

Захват заряда по-прежнему рассматривается как технология будущего для флэш-памяти NAND, но он рассматривается больше для вертикальных структур, чем для плоских ячеек.

Рисунок 4. Процесс сокращается со временем

Рисунок 4. Процесс сокращается со временем Флэш-память NAND масштабируется очень агрессивно (Рисунок 4.) По мере миграции процессов ширина интерфейса управляющего элемента и плавающий затвор сжимается пропорционально квадрату усадки, а расстояние между плавающими затворами сокращается пропорционально усадке процесса, но толщина плавающего затвора остается прежней. (Чем тоньше делается плавающий затвор, тем менее устойчивый к потерям электронов становится ячейка.) Это означает, что связь между соседними плавающими затворами становится больше, чем связь между управляющим затвором и плавающим затвором, что приводит к искажению данных между соседними битами.

Поскольку процессы продолжают сокращаться, это становится все более проблематичным. По этой причине управляющий вентиль в современной флеш-памяти NAND был перенастроен так, чтобы закрывать плавающий вентиль. В конструкции крышки управляющий затвор расширяется, чтобы сформировать барьер между соседними плавающими затворами в обычной ячейке с плавающим затвором (см. Рисунок 5). Это служит для уменьшения связи со смежным плавающим затвором, одновременно увеличивая связь между плавающим затвором и управлением Ворота. Одним из недостатков является то, что управляющий затвор соединяется с каналом, поэтому необходимо принять меры, чтобы минимизировать это соединение.

Рис. 5. Структура ячеек с заглушками для уменьшения емкостной связи между соседними плавающими затворами

Рис. 5. Структура ячеек с заглушками для уменьшения емкостной связи между соседними плавающими затворами В 2006 году считалось, что существующая конструкция крышки с плавающим затвором не может быть изготовлена при процессах, меньших, чем узел 50 нм, из-за трудностей в производстве сложный трехслойный оксид затвора ONO, необходимый для этих устройств.

Samsung даже объявила в конце 2006 г., что к 2008 г. она запустит в производство такое устройство на технологическом узле 40 нм, но за пять лет после этого объявления многие разработчики устройств нашли способы продвигать конструкцию крышки к более широкому использованию. более жесткая геометрия процесса, позволяющая успешно производить NAND размером до 20 нм при таком подходе.

Подход с захватом заряда по-прежнему рассматривается как будущее флэш-памяти NAND для процессов размером менее 20 нм и рассматривается как для плоских, так и для вертикальных трехмерных структур.

Сегодня SanDisk заявляет, что компания рассчитывает продолжить использование обычных структур NAND во втором узле в диапазоне 10–19 нм. Это означает, что стандартные структуры устройств могут оставаться на своих местах до тех пор, пока промышленность не достигнет 10 нм, однако проблемы создания надежного плавающего затвора становятся все более серьезными с каждым сокращением процесса.

С другой стороны, Международная дорожная карта технологий для полупроводников (ITRS) дорожная карта технологических процессов 2010 г. Таблицы интеграции процессов, устройств и структур (PIDS) показывают внедрение улавливания заряда, начиная с 22 нм. в 2012 году и стал массовым в 2014 году благодаря технологии 20 нм.

Возможно, что в будущих процессах будет использоваться ячейка улавливания плоского заряда. Ни один из производителей еще не раскрыл свои процессы для геометрии меньше 19 нм.

Вертикальные структуры рассматриваются как следующий логический шаг для флэш-памяти NAND, когда дальнейшее горизонтальное масштабирование становится невозможным. Поскольку вертикальные элементы не могут быть вытравлены сбоку, слой улавливания заряда становится очень интересным способом создания вертикальной флеш-цепочки NAND.

Toshiba и Samsung Electronics раскрыли прототипы структур NAND с вертикальным захватом заряда.

Toshiba в 2007 году и Samsung в 2009 году объявили о разработке 3D V-NAND, средства построения стандартной строки битов флэш-памяти NAND. вертикально, а не горизонтально, чтобы увеличить количество бит в данной области кремния.

Рис. 6. Вертикальная структура И-НЕ

Рис. 6. Вертикальная структура И-НЕ Примерное представление об этом поперечном сечении показано на рис. 6. На этом чертеже красные части представляют проводящий поликремний, синий - изолирующие слои диоксида кремния, а желтый - слой, улавливающий нитридный заряд.

Вертикальные структуры (показана только одна) представляют собой цилиндры, которые реализуют канал, обернутый чередующимися слоями диэлектрика и улавливания заряда (синего и желтого). Для изготовления такого устройства слои проводящего поликремния и диэлектрика из диоксида кремния сначала наносятся на кремниевую подложку, которая содержит стандартные логические элементы КМОП. Затем канавка протравливается, и на ее стенки наносятся сначала диоксид кремния (синий), затем нитрид кремния (желтый), затем еще один слой диоксида кремния (синий), формирующий диэлектрик затвора, ловушку заряда и туннельный диэлектрик именно в таком порядке. Наконец, отверстие заполняется проводящим поликремнием (красный), который образует канал. Чередующиеся слои проводящего поликремния функционируют как управляющие вентили в этой структуре.

Эта структура использует преимущество того факта, что слой улавливателя заряда не нужно изолировать между каждым управляющим затвором, поэтому его не нужно травить в вертикальном направлении.

Одно из преимуществ флэш-памяти улавливания заряда по сравнению с другими технологиями состоит в том, что ее можно относительно легко встроить с помощью стандартного логического процесса. Стандартный логический процесс можно преобразовать в процесс «логика плюс флэш» путем добавления еще трех масок высокого напряжения и еще трех масок основного CTF, и ни одна из этих шести масок не является критическим уровнем (т. Е. Необходимо использовать наиболее сложную часть процесса.) Все остальные логические процессы могут использоваться напрямую.