В вычислениях, обнаружение последовательного присутствия (SPD ) - это стандартизированный способ автоматического доступа к информации о модуле памяти . Ранние 72-контактные SIMM включали пять контактов, которые обеспечивали пять бит данных параллельного обнаружения присутствия (PPD), но стандарт 168-контактного DIMM был изменен на последовательное обнаружение присутствия для кодирования гораздо большего.

Когда обычный современный компьютер включен, он начинает с выполнения самотестирования при включении (POST). Примерно с середины 1990-х этот процесс включает в себя автоматическую настройку оборудования, имеющегося в настоящее время. SPD - это аппаратная функция памяти, которая позволяет компьютеру узнать, какая память присутствует и какие тайминги памяти использовать для доступа к памяти.

Некоторые компьютеры полностью автоматически адаптируются к изменениям оборудования. В большинстве случаев существует специальная дополнительная процедура для доступа к параметрам BIOS, чтобы просмотреть и, возможно, внести изменения в настройки. Возможно, появится возможность управлять тем, как компьютер использует данные SPD памяти - для выбора настроек, выборочного изменения таймингов памяти или, возможно, для полной отмены данных SPD (см. разгон ).

Для модуля памяти, поддерживающего SPD, стандарты JEDEC требуют, чтобы определенные параметры находились в младших 128 байтах EEPROM находится на модуле памяти. Эти байты содержат параметры синхронизации, производителя, серийный номер и другую полезную информацию о модуле. Устройства, использующие память, автоматически определяют ключевые параметры модуля, считывая эту информацию. Например, данные SPD в модуле SDRAM могут предоставлять информацию о задержке CAS, чтобы система могла правильно установить ее без вмешательства пользователя.

Доступ к SPD EEPROM осуществляется с помощью SMBus, варианта протокола I²C. Это уменьшает количество коммуникационных контактов на модуле до двух: тактовый сигнал и сигнал данных. EEPROM использует общие контакты заземления с RAM, имеет собственный вывод питания и три дополнительных контакта (SA0–2) для идентификации слота, которые используются для присвоения EEPROM уникального адреса в диапазоне 0x50–0x57. Линии связи могут использоваться не только 8 модулями памяти, одна и та же шина SMBus обычно используется на материнских платах для выполнения задач мониторинга состояния системы, таких как считывание напряжений питания, температуры ЦП и скорости вращения вентиляторов.

SPD EEPROM также отвечают на адреса I²C 0x30–0x37, если они не защищены от записи, а расширение (серия TSE) использует адреса 0x18–0x1F для доступа к дополнительному встроенному датчику температуры. Все эти значения представляют собой семибитные адреса I²C, образованные префиксом кода идентификатора типа устройства (DTIC) с SA0-2: для чтения (1100) из слота 3 используется 110 0 011 = 0x33. С последним битом чтения / записи он формирует 8-битный код выбора устройства. Обратите внимание, что семантика идентификатора слота отличается для операций защиты от записи: для них они могут вообще не передаваться контактами SA.

До SPD микросхемы памяти обнаруживались с помощью параллельного обнаружения присутствия (PPD). PPD использовал отдельный вывод для каждого бита информации, что означало, что можно было сохранить только скорость и плотность модуля памяти из-за ограниченного пространства для выводов.

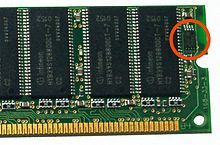

Устройство памяти на модуле SDRAM, содержащее данные SPD (обведено красным)

Устройство памяти на модуле SDRAM, содержащее данные SPD (обведено красным) Первая спецификация SPD была выпущена JEDEC и ужесточена Intel как часть его спецификация памяти PC100. Большинство указанных значений дано в десятичной двоичной форме. Самый значащий полубайт может содержать значения от 10 до 15, а в некоторых случаях может быть выше. В таких случаях вместо этого используются кодировки для 1, 2 и 3 для кодирования 16, 17 и 18. Старший полубайт 0 зарезервирован для представления «неопределенного».

SPD ROM определяет до трех таймингов DRAM для трех задержек CAS, заданных установленными битами в байте 18. Сначала идет самая высокая задержка CAS (самая быстрая тактовая частота), затем две более низкие задержки CAS с постепенно более низкими тактовыми частотами.

| Байт | Бит | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (dec.) | (шестнадцатеричный) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество имеющихся байтов | Обычно 128 | |||||||

| 1 | 0x01 | log 2 (размер SPD EEPROM) | Обычно 8 (256 байтов) | |||||||

| 2 | 0x02 | Базовый тип памяти (4: SPD SDRAM) | ||||||||

| 3 | 0x03 | Биты адреса строки банка 2 (0–15) | Адрес строки банка 1 биты (1–15) | Банк 2 равен 0, если он совпадает с банком 1 | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Столбец банка 1 биты адреса (1–15) | Банк 2 равен 0, если он совпадает с банком 1 | ||||||

| 5 | 0x05 | Количество банков RAM в модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей DIMM с ECC | |||||||

| 7 | 0x07 | Старший байт ширины данных модуля | 0, если ширина ≥ 256 бит | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (не то же самое, что V cc напряжение питания) (0–4) | Декодируется поиском по таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время тактового цикла при максимальной задержке CAS | ||||||

| 10 | 0x0a | Наносекунды (0–15) | Десятые доли наносекунд (0,0 –0.9) | Время доступа к SDRAM с часов (t AC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск в таблице | |||||||

| 12 | 0x0c | Self | Период обновления (0–5): 64, 256, 128, 32, 16, 8 кГц | Требования к обновлению | ||||||

| 13 | 0x0d | Банк 2 2 × | Ширина первичной SDRAM банка 1 (1–127, обычно 8) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2 × | Ширина ECC SDRAM для банка 1 (0–127) | Ширина устройств SDRAM с ECC / четностью банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Тактовая задержка для случайных чтений столбцов | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемые длины пакетов (битовая карта) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 2 или 4 | |||||||

| 18 | 0x12 | — | 7 | 6 | 5 | 4 | 3 | 2 | 1 | Поддерживаются задержки CAS (битовая карта) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки CS (битовая карта) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки WE (растровое изображение) |

| 21 | 0x15 | — | Redundant | Diff. часы | Зарегистрированные данные | Буферизованные данные | ФАПЧ на карте | Зарегистрированный адрес | Буферизованный адрес | Битовая карта функции модуля памяти |

| 22 | 0x16 | — | — | Верхний допуск V cc (напряжение питания) | Нижний допуск V cc (напряжение питания) | Запись / 1 пакет чтения | Предварительная зарядка всех | Автоматическая предварительная зарядка | Ранняя предварительная зарядка RAS | Битовая карта поддержки функции микросхемы памяти |

| 23 | 0x17 | Наносекунды (4–18) | Десятые доли наносекунд (0–9: 0,0–0,9) | Время тактового цикла при средней задержке CAS | ||||||

| 24 | 0x18 | Наносекунды (4–18) | Десятые доли наносекунд (0–9: 0,0–0,9) | Время доступа к данным по часам (t AC) | ||||||

| 25 | 0x19 | Наносекунды ( 1–63) | 0,25 нс (0–3: 0,00–0,75) | Время тактового цикла при короткой задержке CAS. | ||||||

| 26 | 0x1a | наносекунды (1–63) | 0,25 нс (0–3: 0,00–0,75) | Время доступа к данным с часов (t AC) | ||||||

| 27 | 0x1b | Наносекунды (1–255) | Минимальное время предварительной зарядки строки (t RP) | |||||||

| 28 | 0x1c | Na носикунды (1–255) | Минимальная задержка между активной строкой и активной строкой (t RRD) | |||||||

| 29 | 0x1d | Наносекунды (1–255) | Минимум RAS для Задержка CAS (t RCD) | |||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимальное время от активности до предварительной зарядки (t RAS) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МБ | 8 MiB | 4 MiB | Плотность банка модулей (растровое изображение). Установлено два бита, если банки разного размера. |

| 32 | 0x20 | Sign (1: -) | Наносекунды (0–7) | Десятые доли наносекунд (0–9: 0,0–0,9) | Время установки адреса / команды с часов | |||||

| 33 | 0x21 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунд (0–9 : 0,0–0,9) | Время удержания адреса / команды после часов | |||||

| 34 | 0x22 | Знак (1: -) | Наносекунды (0–7) | Десятые доли наносекунд (0–9: 0,0–0,9) | Время установки ввода данных с часов | |||||

| 35 | 0x23 | Знак (1: -) | Наносекунды ( 0–7) | Десятые доли наносекунд (0–9: 0,0–0,9) | Время удержания ввода данных после часов | |||||

| 36–61 | 0x24–0x3d | Зарезервировано | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная версия (0–9) | Дополнительная версия (0–9) | Уровень ревизии СПД; например, 1.2 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не инвертированная затем | |||||||

| 64–71 | 0x40–47 | Идентификатор JEDEC производителя. | Сохраненный прямой порядок байтов, завершающий с нулями | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, дополненный пробелами | |||||||

| 91–92 | 0x5b–0x5c | Модуль код версии | Код производителя | |||||||

| 93 | 0x5d | Десятки лет (0–9: 0–90) | Годы (0–9) | Дата изготовления (YYWW) | ||||||

| 94 | 0x5e | Десятки недель (0–5: 0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f–0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–125 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

| 126 | 0x7e | 0x66 [sic ] для 66 МГц, 0x64 для 100 МГц | Поддержка частоты Intel | |||||||

| 127 | 0x7f | CLK0 | CLK1 | CLK3 | CLK3 | 90/100 ° C | CL3 | CL2 | Concurrent AP | Растровое изображение функций Intel |

Формат DDR DIMM SPD является расширением формата SDR SDRAM. В основном диапазоны параметров масштабируются для соответствия более высоким скоростям.

| Байт | Бит | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| (dec.) | (шестнадцатеричный) | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Количество записанных байтов | Обычно 128 | |||||||

| 1 | 0x01 | журнал 2 (размер SPD EEPROM) | Обычно 8 (256 байтов) | |||||||

| 2 | 0x02 | Базовый тип памяти (7 = DDR SDRAM) | ||||||||

| 3 | 0x03 | Биты адреса строки банка 2 (0–15) | Адрес строки банка 1 биты (1–15) | Банк 2 равен 0, если он совпадает с банком 1. | ||||||

| 4 | 0x04 | Биты адреса столбца банка 2 (0–15) | Банк 1 биты адреса столбца (1–15) | Банк 2 равен 0, если он совпадает с банком 1. | ||||||

| 5 | 0x05 | Количество банков ОЗУ в модуле (1–255) | Обычно 1 или 2 | |||||||

| 6 | 0x06 | Младший байт ширины данных модуля | Обычно 64 или 72 для модулей DIMM с ECC | |||||||

| 7 | 0x07 | Старший байт ширины данных модуля | 0, если ширина ≥ 256 бит | |||||||

| 8 | 0x08 | Уровень напряжения интерфейса этой сборки (не то же самое, что V cc напряжение питания) (0–5) | Декодируется поиском в таблице | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время тактового цикла при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к SDRAM с часов (t AC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск в таблице | |||||||

| 12 | 0x0c | Self | Период обновления (0 –5): 64, 256, 128, 32, 16, 8 кГц | Требования к обновлению | ||||||

| 13 | 0x0d | Банк 2 2 × | Ширина первичного SDRAM банка 1 ( 1–127) | Ширина устройств SDRAM данных банка 1. Банк 2 может иметь одинаковую ширину или 2 × ширину, если установлен бит 7. | ||||||

| 14 | 0x0e | Банк 2 2 × | Ширина ECC SDRAM банка 1 (0–127) | Ширина устройств SDRAM ECC / четности банка 1. Банк 2 может иметь одинаковую ширину или 2-кратную ширину, если установлен бит 7. | ||||||

| 15 | 0x0f | Тактовая задержка для случайных чтений столбцов | Обычно 1 | |||||||

| 16 | 0x10 | Страница | — | — | — | 8 | 4 | 2 | 1 | Поддерживаемые длины пакетов (битовая карта) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 4 | |||||||

| 18 | 0x12 | — | 4 | 3,5 | 3 | 2,5 | 2 | 1,5 | 1 | Поддерживаемые задержки CAS (битовый массив) |

| 19 | 0x13 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддержка задержек CS упорядоченный (растровый) |

| 20 | 0x14 | — | 6 | 5 | 4 | 3 | 2 | 1 | 0 | Поддерживаемые задержки WE (растровое изображение) |

| 21 | 0x15 | — | x | Разностные часы | Внешнее включение переключателя FET | включение переключателя FET на плате | Встроенная ФАПЧ | Зарегистрированная | Буферизованная | Битовая карта функций модуля памяти |

| 22 | 0x16 | Быстрая точка доступа | Параллельная автоматическая предварительная зарядка | Верхний предел V cc (напряжение питания) | Нижний предел V cc (напряжение питания) | — | — | — | Включает слабый драйвер | Битовая карта характеристик микросхемы памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время тактового цикла на среднем уровне Задержка CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (t AC) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время цикла часов при короткой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (t AC) | ||||||

| 27 | 0x1b | наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время предварительной зарядки строки (t RP) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 0,25 нс ( 0–0,75) | Минимальная задержка между активной строкой и активной строкой (t RRD) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 0,25 нс (0– 0,75) | Минимальная задержка от RAS до CAS (t RCD) | ||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимальное время от активного до предварительной зарядки (t RAS) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 64 МБ | 32 МБ | 16 МиБ /. 4 ГиБ | 8 МиБ /. 2 ГиБ | 4 МиБ /. 1 ГиБ | Банковские модули модулей это (растровое изображение). Установлено два бита, если банки разного размера. |

| 32 | 0x20 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время установки адреса / команды с часов | ||||||

| 33 | 0x21 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время удержания адреса / команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время настройки ввода данных с часов | ||||||

| 35 | 0x23 | Десятые доли наносекунд (0,0– 0,9) | Сотые доли наносекунд (0,00–0,09) | Время удержания ввода данных после часов | ||||||

| 36–40 | 0x24–0x28 | Зарезервировано | Информация о расширенном наборе | |||||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности / обновления (t RC) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до времени активности / обновления (t RFC) | |||||||

| 43 | 0x2b | Наносекунды (1–63 или 255: без максимума) | 0,25 нс (0–0,75) | Максимальное время тактового цикла (t CK макс.) | ||||||

| 44 | 0x2c | Сотые доли наносекунды conds (0,01–2,55) | Максимальный перекос, DQS на любой DQ. (t DQSQ макс.) | |||||||

| 45 | 0x2d | Десятые доли наносекунд (0,0–1,2) | Сотые доли наносекунд (0,00–0,09) | Коэффициент перекоса удержания данных при чтении (t QHS) | ||||||

| 46 | 0x2e | Зарезервировано | Для будущей стандартизации | |||||||

| 47 | 0x2f | — | Высота | Высота модуля DIMM, поиск в таблице | ||||||

| 48–61 | 0x30–0x3d | Зарезервировано | Для будущей стандартизации | |||||||

| 62 | 0x3e | Основная версия (0–9) | Незначительная версия (0–9) | Уровень версии SPD, 0,0 или 1,0 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, затем не инвертируется | |||||||

| 64–71 | 0x40–47 | Идентификатор JEDEC производителя. | Хранится с прямым порядком байтов, завершающий с нулями | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, пробел- дополненный | |||||||

| 91–92 | 0x5b–0x5c | Код версии модуля | Код производителя | |||||||

| 93 | 0x5d | Десятки лет (0 –90) | Годы (0–9) | Ману дата производства (YYWW) | ||||||

| 94 | 0x5e | Десятки недель (0–50) | Недели (0–9) | |||||||

| 95–98 | 0x5f – 0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшен профиль производительности | |||||||

Стандарт DDR2 SPD вносит ряд изменений, но примерно аналогичен описанному выше. Одно примечательное исключение - запутанная и мало используемая поддержка модулей DIMM с двумя уровнями разного размера.

Для полей времени цикла (байты 9, 23, 25 и 49), которые закодированы в BCD, некоторые дополнительные кодировки определены для десятых разряда, чтобы точно представить некоторые общие моменты времени:

| Hex | Binary | Значение |

|---|---|---|

| A | 1010 | 0,25 (¼) |

| B | 1011 | 0,33 (⅓) |

| C | 1100 | 0,66 (⅔) |

| D | 1101 | 0,75 (¾) |

| E | 1110 | 0,875 (⅞, расширение nVidia XMP) |

| F | 1111 | Зарезервировано |

| Байт | Бит | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Dec | Hex | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Число записанных байтов | Обычно 128 | |||||||

| 1 | 0x01 | журнал 2 (размер SPD EEPROM) | Обычно 8 ( 256 байт) | |||||||

| 2 | 0x02 | Базовый тип памяти (8 = DDR2 SDRAM) | ||||||||

| 3 | 0x03 | Зарезервировано | Биты адреса строки (1–15) | |||||||

| 4 | 0x04 | Зарезервировано | Биты адреса столбца (1–15) | |||||||

| 5 | 0x05 | Высота по вертикали | Стек? | ConC? | Ранги − 1 (1–8) | Обычно 0 или 1, что означает 1 или 2 | ||||

| 6 | 0x06 | Ширина данных модуля | Обычно 64 или 72 для модулей ECC DIMM | |||||||

| 7 | 0x07 | Зарезервировано | ||||||||

| 8 | 0x08 | Уровень напряжения интерфейса эта сборка (не то же самое, что V cc напряжение питания) (0–5) | Декодируется поиском по таблице.. Обычно 5 = SSTL 1.8 V | |||||||

| 9 | 0x09 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время цикла часов при максимальной задержке CAS. | ||||||

| 10 | 0x0a | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к SDRAM с часов (t AC) | ||||||

| 11 | 0x0b | Тип конфигурации DIMM (0–2): без ECC, четность, ECC | Поиск в таблице | |||||||

| 12 | 0x0c | Self | Период обновления (0 –5): 64, 256, 128, 32, 16, 8 кГц | Требования к обновлению | ||||||

| 13 | 0x0d | Ширина первичной SDRAM (1–255) | Обычно 8 (модуль, состоящий из 8 частей) или 16 | |||||||

| 14 | 0x0e | Ширина ECC SDRAM (0–255) | Ширина банковских устройств SDRAM с ECC / четностью. Обычно 0 или 8. | |||||||

| 15 | 0x0f | Зарезервировано | ||||||||

| 16 | 0x10 | — | — | — | — | 8 | 4 | — | — | Поддерживаемые длины пакетов (битовая карта) |

| 17 | 0x11 | Банков на устройство SDRAM (1–255) | Обычно 4 или 8 | |||||||

| 18 | 0x12 | 7 | 6 | 5 | 4 | 3 | 2 | — | — | Поддерживаемые задержки CAS (растровое изображение) |

| 19 | 0x13 | Зарезервировано | ||||||||

| 20 | 0x14 | — | — | Mini-UDIMM | Mini-RDIMM | Micro-DIMM | SO-DIMM | UDIMM | RDIMM | Тип DIMM этой сборки (bitmap) |

| 21 | 0x15 | — | Модуль анализируется датчик | — | переключатель на полевом транзисторе внешний ena ble | — | — | — | — | Битовая карта функции модуля памяти |

| 22 | 0x16 | — | — | — | — | — | — | — | Включает слабый драйвер | битовая карта функции микросхемы памяти |

| 23 | 0x17 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время тактового цикла при средней задержке CAS. | ||||||

| 24 | 0x18 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (t AC) | ||||||

| 25 | 0x19 | Наносекунды (0–15) | Десятые доли наносекунд (0,0–0,9) | Время цикла часов при короткой задержке CAS. | ||||||

| 26 | 0x1a | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время доступа к данным с часов (t AC) | ||||||

| 27 | 0x1b | наносекунды (1–63) | 1/4 нс (0–0,75) | Минимальное время предварительной зарядки строки (t RP) | ||||||

| 28 | 0x1c | Наносекунды (1–63) | 1 / 4 нс (0–0,75) | Минимальная задержка между активной строкой и активной строкой (t RRD) | ||||||

| 29 | 0x1d | Наносекунды (1–63) | 1 / 4 нс (0–0,75) | Минимальная задержка от RAS до CAS (t RCD) | ||||||

| 30 | 0x1e | Наносекунды (1–255) | Минимум активного до время предварительной зарядки (t RAS) | |||||||

| 31 | 0x1f | 512 МБ | 256 МБ | 128 МБ | 16 ГБ | 8 ГиБ | 4 ГиБ | 2 ГиБ | 1 ГиБ | Размер каждого ранга (битовая карта). |

| 32 | 0x20 | Десятый с наносекунд (0,0–1,2) | Сотые доли наносекунд (0,00–0,09) | Время установки адреса / команды с часов | ||||||

| 33 | 0x21 | Десятые доли наносекунд (0,0 –1.2) | Сотые доли наносекунд (0,00–0,09) | Время удержания адреса / команды после часов | ||||||

| 34 | 0x22 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунд (0,00–0,09) | Время настройки ввода данных из строба | ||||||

| 35 | 0x23 | Десятые доли наносекунд (0,0–0,9) | Сотые доли наносекунды (0,00–0,09) | Время удержания ввода данных после строба | ||||||

| 36 | 0x24 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Минимальное время восстановления записи (t WR) | ||||||

| 37 | 0x25 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутренняя задержка команды записи для чтения (t WTR) | ||||||

| 38 | 0x26 | Наносекунды (1–63) | 0,25 нс (0–0,75) | Внутреннее чтение для задержки команды предварительной зарядки (t RTP) | ||||||

| 39 | 0x27 | Зарезервировано | Зарезервировано для «характеристик зонда анализа памяти» | |||||||

| 40 | 0x28 | — | tRCдробное нс (0 –5):. 0, 0,25, 0,33, 0,5, 0,66, 0,75 | tRFC дробные нс (0–5):. 0, 0,25, 0,33, 0,5, 0,66, 0,75 | tRFC + 256 нс | Расширение байтов 41 и 42. | ||||

| 41 | 0x29 | Наносекунды (1–255) | Минимальное время активности / обновления ( t RC) | |||||||

| 42 | 0x2a | Наносекунды (1–255) | Минимальное время обновления до активного / времени обновления (t RFC) | |||||||

| 43 | 0x2b | Наносекунды (0– 15) | Десятые доли наносекунд (0,0–0,9) | Максимальное время тактового цикла (t CK max) | ||||||

| 44 | 0x2c | Сотые доли наносекунд (0,01–2,55) | Максимальный перекос, DQS на любой DQ. (t DQSQ max) | |||||||

| 45 | 0x2d | Сотые доли наносекунд (0,01–2,55) | Коэффициент перекоса удержания считанных данных (t QHS) | |||||||

| 46 | 0x2e | Микросекунды (1–255) | Время повторной синхронизации PLL | |||||||

| 47–61 | 0x2f–0x3d | Зарезервировано | Для будущая стандартизация. | |||||||

| 62 | 0x3e | Основная версия (0–9) | Незначительная версия (0,0–0,9) | Уровень версии SPD, обычно 1.0 | ||||||

| 63 | 0x3f | Контрольная сумма | Сумма байтов 0–62, не инвертированная | |||||||

| 64–71 | 0x40–47 | Производитель JEDEC ID | Сохраненный прямой порядок байтов, завершающий нулевой блок | |||||||

| 72 | 0x48 | Место изготовления модуля | Код производителя | |||||||

| 73–90 | 0x49–0x5a | Номер детали модуля | ASCII, заполненный пробелами (ограничен (, -,), A – Z, a – z, 0–9, пробел) | |||||||

| 91–92 | 0x5b–0x5c | Код версии модуля | Код производителя | |||||||

| 93 | 0x5d | Годы с 2000 г. (0–255) | Производство дата (ГГГП) | |||||||

| 94 | 0x5e | Недели (1–52) | ||||||||

| 95–98 | 0x5f – 0x62 | Серийный номер модуля | Код производителя | |||||||

| 99–127 | 0x63–0x7f | Данные производителя | Может быть улучшенным профиль производительности | |||||||

Стандарт DDR3 SDRAM значительно пересматривает и упрощает структуру содержимого SPD. Вместо ряда наносекундных полей в кодировке BCD некоторые единицы «временной развертки» задаются с высокой точностью, а различные параметры синхронизации кодируются как кратные этой базовой единице. Кроме того, отказались от практики указания различных значений времени в зависимости от задержки CAS; теперь есть только один набор временных параметров.

Версия 1.1 позволяет выражать некоторые параметры как значение «средней временной развертки» плюс (со знаком, −128 +127) «точную временную развертку» поправки. Обычно средняя временная развертка составляет 1/8 нс (125 пс), а точная временная развертка составляет 1, 2,5 или 5 пс. Для совместимости с более ранними версиями, в которых отсутствует коррекция, среднее значение временной базы обычно округляется в большую сторону, а коррекция отрицательная. Значения, которые работают таким образом:

| байт MTB | байт FTB | значение |

|---|---|---|

| 12 | 34 | tCKмин, минимальный период тактовой частоты |

| 16 | 35 | tAAмин, минимальное время задержки CAS |

| 18 | 36 | tRCD мин, минимальная задержка от RAS # до CAS # |

| 20 | 37 | tRPмин, минимальная задержка предварительной зарядки строки |

| 21, 23 | 38 | tRCмин, минимальная задержка от активного до активного / предварительной зарядки |

| Байт | Бит | Примечания | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Dec | Hex | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | Исключить серийный номер из CRC | Всего байт SPD (undef / 256) | использованных байтов SPD (undef / 128/176/256) | ||||||

| 1 | 0x01 | основная версия SPD | SPD младшая версия | 1.0, 1.1, 1.2 или 1.3 | ||||||

| 2 | 0x02 | Базовый тип памяти (11 = DDR3 SDRAM) | Тип микросхем RAM | |||||||

| 3 | 0x03 | Зарезервировано | Тип модуля | Тип модуля; например, 2 = небуферизованный DIMM, 3 = SO-DIMM, 11 = LRDIMM | ||||||

| 4 | 0x04 | — | Биты адреса банка-3 | log 2 (бит на чип) -28 | Ноль означает 8 банков, 256 Mibit. | |||||

| 5 | 0x05 | — | Биты адреса строки-12 | Биты адреса столбца-9 | ||||||

| 6 | 0x06 | Зарезервировано | 1,25 В | 1,35 В | Не 1,5 В | Поддерживаемые напряжения модулей. 1,5 В. По умолчанию. | ||||

| 7 | 0x07 | — | ranks−1 | log 2 (I / O бит / чип) −2 | Организация модуля | |||||

| 8 | 0x08 | — | ECC биты (001 = 8) | log 2 (биты данных) −3 | 0x03 для 64-битных модулей DIMM без ECC. | |||||

| 9 | 0x09 | Дивиденд, пикосекунды (1–15) | Делитель, пикосекунды (1–15) | Точная временная база, деление / делитель | ||||||

| 10 | 0x0a | Дивиденд, наносекунды (1–255) | Средняя временная база, делимое / делитель; обычно 1/8 | |||||||

| 11 | 0x0b | Делитель, наносекунды (1–255) | ||||||||

| 12 | 0x0c | Минимальное время цикла t CK мин | Кратно MTB | |||||||

| 13 | 0x0d | Зарезервировано | ||||||||

| 14 | 0x0e | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | Поддерживаемые задержки CAS (растровое изображение) |

| 15 | 0x0f | — | 18 | 17 | 16 | 15 | 14 | 13 | 12 | |

| 16 | 0x10 | Минимальное время задержки CAS, t AA min | В кратных MTB; например, 80/8 нс. | |||||||

| 17 | 0x11 | Минимальное время восстановления при записи, t WR мин | В кратных MTB; например, 120/8 нс. | |||||||

| 18 | 0x12 | Минимальное время задержки от RAS до CAS, t RCD мин | В кратных значениях MTB; например, 100/8 нс. | |||||||

| 19 | 0x13 | Минимальное время активной задержки от строки к строке, t RRD min | В кратных MTB; например, 60/8 нс. | |||||||

| 20 | 0x14 | Минимальное время предварительной зарядки строки, t RP мин | В кратных MTB; например, 100/8 нс. | |||||||

| 21 | 0x15 | tRCmin, биты 11: 8 | tRAS min, биты 11: 8 | Старшие 4 бита байтов 23 и 22 | ||||||

| 22 | 0x16 | Минимальное время активности, t RAS мин, биты 7: 0 | В кратных MTB; например, 280/8 нс. | |||||||

| 23 | 0x17 | Минимум от активного до активного / обновления, t RC мин, биты 7: 0 | В кратных MTB; например, 396/8 нс. | |||||||

| 24 | 0x18 | Минимальная задержка восстановления при обновлении, t RFC мин, биты 7: 0 | В кратных MTB; например, 1280/8 нс. | |||||||

| 25 | 0x19 | Минимальная задержка восстановления восстановления, t RFC min, биты 15: 8 | ||||||||

| 26 | 0x1a | Минимальная внутренняя задержка от записи до чтения, t WTR min | В кратных MTB; например, 60/8 нс. | |||||||

| 27 | 0x1b | Минимальное внутреннее считывание до задержки предварительной зарядки, t RTP мин | В кратных MTB; например, 60/8 нс. | |||||||

| 28 | 0x1c | Зарезервировано | tFAW мин, биты 11: 8 | В кратных значениях MTB; например, 240/8 нс. | ||||||

| 29 | 0x1d | Минимум четыре задержки окна активации t FAW min, биты 7: 0 | ||||||||

| 30 | 0x1e | DLL-off | — | RZQ / 7 | RZQ / 6 | Дополнительные функции SDRAM поддерживают растровое изображение | ||||

| 31 | 0x1f | PASR | — | ODTS | ASR | ETR 1 × | ETR (95 ° C) | Параметры охлаждения и восстановления SDRAM | ||

| 32 | 0x20 | Present | Точность (TBD; в настоящее время 0 = не определено) | присутствует термодатчик DIMM? | ||||||

| 33 | 0x21 | Nonstd. | Количество кристаллов | — | Сигнальная нагрузка | Нестандартный тип устройства SDRAM (например, сложенный кристалл) | ||||

| 34 | 0x22 | tCKмин. Коррекция (новое для версии 1.1) | Знаковое кратное FTB, добавленное к байту 12 | |||||||

| 35 | 0x23 | tAAмин. коррекция (новое для 1.1) | Подписанное кратное FTB, добавленное к байту 16 | |||||||

| 36 | 0x24 | tУЗО мин. Коррекция (новая для 1.1) | Знаковое кратное FTB, добавленное к байту 18 | |||||||

| 37 | 0x25 | tRPмин. Коррекция (новое для 1.1) | Знаковое кратное FTB, добавленное к байту 20 | |||||||

| 38 | 0x26 | tRCмин. Поправка (новое для 1.1) | Знаковое кратное FTB, добавленное к байту 23 | |||||||

| 39–40 | 0x27–0x28 | Зарезервировано | Для будущей стандартизации. | |||||||

| 41 | 0x29 | Зависит от поставщика | tMAW | Максимальный счетчик активации (MAC) (непроверено / 700k / 600k /.../ 200k / зарезервировано / ∞) | Для рядный молоток смягчение последствий | |||||

| 42–59 | 0x2a–0x3b | Зарезервировано | Для будущей стандартизации. | |||||||

| 60 | 0x3c | — | Высота модуля, мм (1–31,>45) | Номинальная высота модуля | ||||||

| 61 | 0x3d | Толщина задней стенки, мм (1–16) | Толщина фасада, мм (1–16) | Толщина модуля, значение = ceil (мм) - 1 | ||||||

| 62 | 0x3e | Дизайн | Ревизия | Номер проекта JEDEC | Используется эталонный дизайн JEDEC (11111 = нет) | |||||

| 63–116 | 0x3f–0x74 | Раздел для конкретного модуля | Различается между зарегистрированным / небуферизованным | |||||||

| 117 | 0x75 | ID производителя модуля, лсбайт | Назначено JEP-106 | |||||||

| 118 | 0x76 | Идентификатор производителя модуля, мсбайт | ||||||||

| 119 | 0x77 | Место изготовления модуля | Код производителя | |||||||

| 120 | 0x78 | Десятки лет | Годы | Год изготовления (BCD) | ||||||

| 121 | 0x79 | Десятки недель | Недели | Производственная неделя (BCD) | ||||||

| 122–125 | 0x7a–0x7d | Серийный номер модуля | Производитель- специальный код | |||||||

| 126–127 | 0x7e–0x7f | S PD CRC-16 | Включает байты 0–116 или 0–125; см. байт 0 бит 7 | |||||||

| 128–145 | 0x80–0x91 | Номер детали модуля | подмножество ASCII, дополненное пробелами | |||||||

| 146–147 | 0x92–0x93 | Код версии модуля | Определяется производителем | |||||||

| 148–149 | 0x94–0x95 | ID производителя DRAM | В отличие от производителя модуля | |||||||

| 150–175 | 0x96–0xAF | Данные производителя | ||||||||

| 176–255 | 0xB0–0xFF | Доступно для использования заказчиком | ||||||||

Емкость памяти модуля может быть вычислена из байтов 4, 7 и 8. Ширина модуля (байт 8), деленная на количество бит на чип (байт 7), дает количество фишек на ранг. Затем это можно умножить на емкость каждого чипа (байт 4) и количество рангов чипов в модуле (обычно 1 или 2, начиная с байта 7).

Стандарт DDR4 SDRAM "Annex L" для SPD изменяет используемый модуль EEPROM. Instead of the old AT24C02-compatible 256-byte EEPROMs, JEDEC now defines a new nonstandard EE1004 type with two pages at the SMBus level each with 256 bytes. The new memory still uses the old 0x50-0x57 addresses, but two additional address at 0x36 (SPA0) and 0x37 (SPA1) are now used to receive commands to select the currently-active page for the bus, a form of bank switching. Internally each logical page is further divided into two physical blocks of 128 bytes each, totaling four blocks and 512 bytes. Other semantics for "special" address ranges remain the same, although write protection is now addressed by blocks and a high voltage at SA0 is now required to change its status.

Annex L defines a few different layouts that can be plugged into a 512-byte (of which a maximum of 320 bytes are defined) template, depending on the type of the memory module. The bit definitions are similar to DDR3.

| Byte | Bit | Notes | ||||||||

|---|---|---|---|---|---|---|---|---|---|---|

| Dec | Hex | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | |

| 0 | 0x00 | SPD bytes used | ||||||||

| 1 | 0x01 | SPD revision n | Typically 0x10, 0x11, 0x12 | |||||||

| 2 | 0x02 | Basic memory type (12 = DDR4 SDRAM) | Type of RAM chips | |||||||

| 3 | 0x03 | Reserved | Module type | Type of module; e.g., 2 = Unbuffered DIMM, 3 = SO-DIMM, 11=LRDIMM | ||||||

| 4 | 0x04 | Bank group bits | Bank address bits−2 | Total SDRAM capacity per die in Mb | Zero means no bank groups, 4 banks, 256 Mibit. | |||||

| 5 | 0x05 | Reserved | Row address bits−12 | Column address bits−9 | ||||||

| 6 | 0x06 | Primary SDRAM package type | Die count | Reserved | Signal loading | |||||

| 7 | 0x07 | Reserved | Maximum activate window (tMAW) | Maximum activate count (MAC) | SDRAM optional features | |||||

| 8 | 0x08 | Reserved | SDRAM thermal and refresh options | |||||||

| 9 | 0x09 | Post package repair (PPR) | Soft PPR | Reserved | Other SDRAM optional features | |||||

| 10 | 0x0a | SDRAM package type | Die count−1 | DRAM density ratio | Signal loading | Secondary SDRAM package type | ||||

| 11 | 0x0b | Reserved | Endurant flag | Operable flag | Module nominal voltage, VDD | |||||

| 12 | 0x0c | Reserved | Rank mix | Package ranks per DIMM−1 | SDRAM device width | Module organization | ||||

| 13 | 0x0d | Reserved | Bus width extension | Primary bus width | M odule memory bus width in bits | |||||

| 14 | 0x0e | Thermal sensor | Reserved | Module thermal sensor | ||||||

| 15 | 0x0f | Reserved | Extended base module type | |||||||

| 16 | 0x10 | Reserved | ||||||||

| 17 | 0x11 | Reserved | Medium timebase (MTB) | Fine timebase (FTB) | Measured in ps. | |||||

| 18 | 0x12 | Minimum SDRAM cycle time, tCKAVGmin | In multiples of MTB; e.g., 100/8 ns. | |||||||

| 19 | 0x13 | Maximum SDRAM cycle time, tCKAVGmax | In multiples of MTB; e.g., 60/8 ns. | |||||||

| 20 | 0x14 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | CAS latencies supported bit-mask |

| 21 | 0x15 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | CAS latencies supported bit-mask |

| 22 | 0x16 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | CAS latencies supported bit-mask |

| 23 | 0x17 | Low CL range | Reserved | 36 | 35 | 34 | 33 | 32 | 31 | CAS latencies supported bit-mask |

| 24 | 0x18 | Minimum CAS latency time, tAAmin | In multiples of MTB; e.g., 1280/8 ns. | |||||||

| 25 | 0x19 | Minimum RAS to CAS delay time, tRFCmin | In multiples of MTB; e.g., 60/8 ns. | |||||||

| 26 | 0x1a | Minimum row precharge delay time, tRPmin | In multiples of MTB; e.g., 60/8 ns. | |||||||

| 27 | 0x1b | Upper nibbles for tRASmin and tRCmin | ||||||||

| 28 | 0x1c | Minimum active to precharge delay time, tRASmin least significant byte | In multiples of MTB | |||||||

| 29 | 0x1d | Minimum active to active/refresh delay time, tRCmin least significant byte | In multiples of MTB | |||||||

| 30 | 0x1e | Minimum refresh recovery delay time, tRFC1min least significant byte | In multiples of MTB | |||||||

| 31 | 0x1f | Minimum refresh recovery delay time, tRFC1min most significant byte | In multiples of MTB | |||||||

| 32 | 0x20 | Minimum refresh recovery delay time, tRFC2min least significant byte | In multiples of MTB | |||||||

| 33 | 0x21 | Minimum refresh recovery delay time, tRFC2min most significant byte | In multiples of MTB | |||||||

| 34 | 0x22 | Minimum refresh recovery delay time, tRFC4min least significant byte | In multiples of MTB | |||||||

| 35 | 0x23 | Minimum refresh rec overy delay time, tRFC4min most significant byte | In multiples of MTB | |||||||

| 36 | 0x24 | Reserved | tFAWmin most significant nibble | |||||||

| 37 | 0x25 | Minimum four activate window delay time, tFAWm в младшем значащем байте | Кратно MTB | |||||||

| 38 | 0x26 | Минимальное время активации для активации задержки, t RRD_S мин, другая группа банков | Кратно MTB | |||||||

| 39 | 0x27 | Минимальное время активации для активации задержки, t RRD_S мин, та же группа банков | Кратно MTB | |||||||

| 40 | 0x28 | Минимальное время задержки CAS в CAS, t CCD_L мин, та же группа банков | В кратных MTB | |||||||

| 41 | 0x29 | Верхний полубайт для t WR min | ||||||||

| 42 | 0x2a | Минимальное время восстановления записи, t WR min | В кратных MTB | |||||||

| 43 | 0x2b | Верхние полубайты для t WTR min | ||||||||

| 44 | 0x2c | Минимальное время записи для чтения, t WTR_S min, другая группа банков | В кратных MTB | |||||||

| 45 | 0x2d | Минимальное время записи для чтения, t WTR_L мин, та же группа банков | В кратных MTB | |||||||

| 49–59 | 0x2e – 0x3b | Зарезервировано | Раздел базовой конфигурации | |||||||

| 60-77 | 0x3c-0x4d | Соединитель с SDRAM бит m apping | ||||||||

| 78–116 | 0x4e–0x74 | Reserved | Раздел базовой конфигурации | |||||||

| 117 | 0x75 | Fine смещение минимального времени задержки CAS в CAS, t CCD_L мин, тот же банк | Дополнительный множитель до двух для блоков FTB | |||||||

| 118 | 0x76 | Точное смещение для минимальной активации для активации времени задержки, t RRD_L мин, та же группа банков | Двукратный множитель для блоков FTB | |||||||

| 119 | 0x77 | Точное смещение для минимальной активации для активации времени задержки, t RRD_S мин, другая группа банков | Множитель с дополнением до двух для блоков FTB | |||||||

| 120 | 0x78 | Точное смещение для минимального времени задержки между активным и активным / обновлением, t RC min | Множитель с дополнением до двух для блоков FTB | |||||||

| 121 | 0x79 | Точное смещение для минимального времени задержки предварительной зарядки строки, t RP min | Множитель с дополнением до двух для блоков FTB | |||||||

| 122 | 0x7a | Точное смещение для минимального времени задержки от RAS к CAS, t RCD min | Множитель с дополнением до двух для блоков FTB | |||||||

| 123 | 0x7b | Точное смещение для минимального времени задержки CAS, t AA min | Множитель с дополнением до двух для блоков FTB | |||||||

| 124 | 0x7c | Точное смещение для максимального времени цикла SDRAM, t CKAVG max | Множитель с дополнением до двух для блоков FTB | |||||||

| 125 | 0x7d | Точное смещение для минимального времени цикла SDRAM, t CKAVG мин | Множитель с дополнением до двух для блоков FTB | |||||||

| 126 | 0x7e | Циклический код избыточности (CRC) для раздела базовой конфигурации, младший байт | Алгоритм CRC16 | |||||||

| 127 | 0x7f | Циклический код избыточности (CRC) для раздела базовой конфигурации, старший байт | Алгоритм CRC16 | |||||||

| 128–191 | 0x80–0xbf | Специфичный для модуля раздел | Зависит от семейства модулей памяти (UDIMM, RDIMM, LRDIMM) | |||||||

| 192–255 | 0xc0–0xff | Гибрид параметры архитектуры памяти | ||||||||

| 256–319 | 0x100–0x13f | Блок параметров расширенной функции | ||||||||

| 320-321 | 0x140-0x141 | Производитель модуля | См. JEP-106 | |||||||

| 322 | 0x142 | Место изготовления модуля | Код места производства, определенный производителем | |||||||

| 323 | 0x143 | Модуль Год изготовления | Представлен в десятичном формате с двоичным кодом (BCD) | |||||||

| 324 | 0x144 | Неделя изготовления модуля | Представлен в десятичном формате с двоичным кодом (BCD) | |||||||

| 325-328 | 0x145-0x148 | Серийный номер модуля | Определенный производителем формат уникального серийного номера для номеров деталей | |||||||

| 329-348 | 0x149-0x15c | Номер детали модуля | Номер детали ASCII, неиспользуемые цифры должны быть установлены на 0x20 | |||||||

| 349 | 0x15d | Код версии модуля | Код версии, определенный производителем | |||||||

| 350-351 | 0x15e-0x15f | Идентификационный код производителя DRAM | См. JEP-106 | |||||||

| 352 | 0x160 | Степпинг DRAM | Определенный производителем шаг или 0xFF, если не используется | |||||||

| 353–381 | 0x161–0x17d | Данные производителя | ||||||||

| 382–383 | 0x17e-0x17f | Зарезервировано | ||||||||

Стандарт JEDEC определяет только некоторые байты SPD. По-настоящему важные данные помещаются в первые 64 байта, а некоторые из оставшихся предназначены для идентификации производителя. Однако обычно предоставляется 256-байтовая EEPROM. Оставшееся пространство было использовано в ряде случаев.

Память обычно поставляется с консервативными рекомендациями по времени в SPD ROM, чтобы обеспечить базовую функциональность во всех системах. Энтузиасты часто тратят много времени на ручную настройку таймингов памяти для повышения скорости.

Enhanced Performance Profiles - это расширение SPD, разработанное Nvidia и Corsair, которое включает дополнительную информацию для более высокопроизводительной работы DDR2 SDRAM, включая данные о напряжениях питания и времени команд, не включенные в спецификацию JEDEC SPD. Информация EPP хранится в той же EEPROM, но в байтах 99-127, которые не используются стандартной DDR2 SPD.

| Байт | Размер | Полный профили | Сокращенные профили |

|---|---|---|---|

| 99–103 | 5 | Заголовок EPP | |

| 104–109 | 6 | Профиль FP1 | Профиль AP1 |

| 110–115 | 6 | Профиль AP2 | |

| 116–121 | 6 | Профиль FP2 | Профиль AP3 |

| 122–127 | 6 | Профиль AP4 | |

Параметры специально разработаны для соответствия контроллеру памяти на nForce 5, чипсеты nForce 6 и nForce 7. Nvidia поощряет поддержку EPP в BIOS для своих высокопроизводительных наборов микросхем материнских плат. Это предназначено для обеспечения "разгона одним щелчком мыши " для повышения производительности с минимальными усилиями.

Nvidia называет память EPP, аттестованную по производительности и стабильности, «память с поддержкой SLI». Термин «память, готовая к SLI» вызвал некоторую путаницу, поскольку он не имеет ничего общего с SLI video. Можно использовать память EPP / SLI с одной видеокартой (даже с картой, отличной от Nvidia), и можно запустить настройку видео SLI с несколькими картами без памяти EPP / SLI.

Расширенная версия EPP 2.0 также поддерживает память DDR3.

Аналогичный, разработанный Intel JEDEC Расширение SPD было разработано для модулей DIMM DDR3 SDRAM, которое позже также использовалось в DDR4. XMP использует байты 176–255, которые не выделяются JEDEC, для кодирования таймингов памяти с более высокой производительностью.

Позже AMD разработала AMP, технологию, эквивалентную XMP, для использования в линейке памяти «Radeon Memory» модули оптимизированы для использования на платформах AMD. Кроме того, разработчики материнских плат внедрили свои собственные технологии, позволяющие материнским платам на базе AMD читать профили XMP: MSI предлагает A-XMP, ASUS имеет DOCP (динамические профили разгона), а Gigabyte имеет EOCP (расширенные профили разгона).

| Байт DDR3 | Размер | Использовать |

|---|---|---|

| 176–184 | 10 | Заголовок XMP |

| 185–219 | 33 | Профиль XMP 1 («энтузиаст» настройки) |

| 220–254 | 36 | Профиль XMP 2 («экстремальные» настройки) |

Заголовок содержит следующие данные. Наиболее важно то, что он содержит значение MTB для «средней временной развертки» как рациональное количество наносекунд (общие значения - 1/8, 1/12 и 1/16 нс). Многие другие более поздние значения синхронизации выражаются целым числом единиц MTB.

В заголовок также включено количество модулей DIMM на канал памяти, для поддержки которых предназначен профиль; включение большего количества модулей DIMM может не работать.

| Байт DDR3 | Биты | Используйте |

|---|---|---|

| 176 | 7:0 | XMP магическое число байт 1 0x0C |

| 177 | 7:0 | байт 2 магического числа XMP 0x4A |

| 178 | 0 | Профиль 1 включен (если 0, отключен) |

| 1 | Профиль 2 включен | |

| 3:2 | Профиль 1 DIMM на канал (1–4 с кодировкой 0–3) | |

| 5:4 | Профиль 2 модуля DIMM на канал | |

| 7: 6 | Зарезервировано | |

| 179 | 3:0 | Дополнительный номер версии XMP (x.0 или x.1) |

| 7: 4 | Основной номер версии XMP (0.x или 1.x) | |

| 180 | 7:0 | Средний дивиденд по временной развертке для профиля 1 |

| 181 | 7: 0 | Средний делитель временной развертки для профиля 1 (MTB = делитель / делитель нс) |

| 182 | 7:0 | Средний делитель временной развертки для профиля 2 (например, 8) |

| 183 | 7:0 | Средний делитель временной развертки для профиля 2 (например, 1, что дает MTB = 1/8 нс) |

| 184 | 7: 0 | Зарезервировано |

| Байт 1 DDR3 | Байт 2 DDR3 | Биты | Использовать |

|---|---|---|---|

| 1 85 | 220 | 0 | Напряжение Vdd модуля, двадцатых (0,00 или 0,05) |

| 4:1 | Напряжение Vdd модуля, десятые доли (0,0–0,9) | ||

| 6: 5 | Модуль Vdd, единицы напряжения (0–2) | ||

| 7 | Зарезервировано | ||

| 186 | 221 | 7:0 | Минимальный период тактовой частоты SDRAM t CK мин (единицы MTB) |

| 187 | 222 | 7:0 | Минимальное время задержки CAS t AA мин (MTB единиц) |

| 188 | 223 | 7:0 | Поддерживаемые задержки CAS (битовая карта, 4–11, закодированные как биты 0–7) |

| 189 | 224 | 6: 0 | Поддерживаемые задержки CAS (битовая карта, 12–18, закодированные как биты 0–6) |

| 7 | Зарезервировано | ||

| 190 | 225 | 7: 0 | Минимальное время задержки записи CAS t CWL мин (единицы MTB) |

| 191 | 226 | 7: 0 | Минимальное время задержки предварительной зарядки строки t RP мин (единицы MTB) |

| 192 | 227 | 7: 0 | Минимальное время задержки от RAS до CAS t RCD мин (единицы MTB) |

| 193 | 228 | 7:0 | Минимум время восстановления записи t WR мин (MTB единиц) |

| 194 | 229 | 3: 0 | tRAS мин. верхний полубайт (биты 11: 8) |

| 7: 4 | tRCмин. Верхний полубайт (биты 11: 8) | ||

| 195 | 230 | 7:0 | Минимальное время задержки активного до предварительной зарядки t RAS мин. Биты 7: 0 (единицы MTB) |

| 196 | 231 | 7:0 | Минимальное время задержки между активным и активным / обновлением t RC мин. Биты 7: 0 (единицы MTB) |

| 197 | 232 | 7:0 | Максимальный средний интервал обновления t REFI lsbyte (единицы MTB) |

| 198 | 233 | 7:0 | Максимальный средний интервал обновления t REFI msbyte (единицы MTB) |

| 199 | 234 | 7: 0 | Минимальное время задержки восстановления при обновлении t RFC мин. Lsbyte (единицы MTB) |

| 200 | 235 | 7:0 | Минимальное время задержки восстановления восстановления t RFC мин мсбайт (единицы MTB) |

| 201 | 236 | 7: 0 | Минимальное внутреннее считывание до времени задержки команды предварительной зарядки t RTP мин (единицы MTB) |

| 202 | 237 | 7: 0 | Минимальная строка, активная для активного времени задержки строки t RRD мин (единицы MTB) |

| 203 | 238 | 3: 0 | tFAW мин верхний полубайт (биты 11: 8) |

| 7:4 | Зарезервировано | ||

| 204 | 239 | 7:0 | Активировать минимум четыре время задержки окна t FAW мин. биты 7: 0 (единицы MTB) |

| 205 | 240 | 7:0 | Минимальная внутренняя запись в время задержки команды чтения t WTR мин (единицы MTB) |

| 206 | 241 | 2:0 | Запись для регулировки времени выполнения команды чтения (0–7 тактов) |

| 3 | Запись для считывания знака настройки времени выполнения команды (0 = втягивание, 1 = выталкивание) | ||

| 6:4 | Чтение для записи настройки времени выполнения команды ( 0–7 тактов) | ||

| 7 | Чтение для записи знака регулировки поворота команды (0 = втягивание, 1 = выталкивание) | ||

| 207 | 242 | 2: 0 | Последовательная регулировка времени выполнения команд (0–7 тактовых циклов) |

| 3 | Знак последовательной регулировки времени выполнения (0 = втягивание, 1 = выталкивание) | ||

| 7: 4 | Зарезервировано | ||

| 208 | 243 | 7:0 | Режим скорости системного CMD. 0 = JTAG по умолчанию, в противном случае в особых единицах MTB × t CK / нс.. Например. если MTB составляет 1/8 нс, то это единицы 1/8 тактового цикла. |

| 209 | 244 | 7:0 | Производительность автообновления SDRAM.. В стандартной версии 1.1 указано, что документация TBD. |

| 210– 218 | 245–253 | 7: 0 | Зарезервировано |

| 219 | 254 | 7: 0 | Зарезервированный индивидуальный код поставщика. |

Все данные выше относятся к DDR3 (XMP 1.1); Спецификации DDR4 пока недоступны.

Распространенным неправильным использованием является запись информации в определенные области памяти для привязки модулей памяти конкретного производителя к определенной системе. Fujitsu Technology Solutions, как известно, делает это. Добавление другого модуля памяти в систему обычно приводит к отказу или другим ответным мерам (например, нажатие F1 при каждой загрузке).

02 0E 00 01-00 00 00 EF-02 03 19 4D-BC 47 C3 46........... MGF 53 43 00 04-EF 4F 8D 1F-00 01 70 00-01 03 C1 CF SC... O.... p.....

Это результат модуля памяти на 512 МБ от Micron Technologies, выпускаемого Fujitsu-Siemens Computers, обратите внимание на Строка «FSC». Системная BIOS отклоняет модули памяти, в которых нет этой информации, начиная со смещения 128h.

Некоторые ноутбуки Packard Bell AMD также используют этот метод, в этом случае симптомы могут различаться, но это может привести к миганию курсора, а не к звуковому сигналу. Кстати, это тоже может быть признаком повреждения BIOS. Хотя обновление 2 ГБ до 4 ГБ также может привести к проблемам.

Производители модулей памяти записывают информацию SPD в EEPROM на модуле. Материнская плата BIOS считывает информацию SPD для настройки контроллера памяти. Существует несколько программ, которые могут считывать и изменять информацию SPD на большинстве, но не на всех наборах микросхем материнских плат.

Независимое от набора микросхем чтение и запись Информация SPD осуществляется путем доступа к EEPROM памяти напрямую с помощью аппаратного и программного обеспечения программатора eeprom.

Не так часто используются старые портативные компьютеры в качестве обычных считывателей SMBus, поскольку внутренняя EEPROM на модуле может быть отключена после того, как BIOS ее прочитает, так что шина практически доступна для использования. Используемый метод заключается в понижении уровня линий A0, A1, чтобы внутренняя память отключилась, позволяя внешнему устройству получить доступ к SMBus. Как только это будет сделано, пользовательская сборка Linux или приложение DOS сможет получить доступ к внешнему устройству. Обычно используется восстановление данных с микросхем памяти ЖК-панелей для модернизации стандартной панели в проприетарном ноутбуке. На некоторых микросхемах также рекомендуется разделить линии защиты от записи, чтобы встроенные микросхемы не стирались во время перепрограммирования. Связанный с этим метод заключается в перезаписи чипа на веб-камерах, которые часто входят во многие ноутбуки, поскольку скорость шины значительно выше и может даже быть изменена, чтобы 25x совместимые чипы могли быть считаны для последующего клонирования uEFI в случае отказа чипа.

Это, к сожалению, работает только с DDR3 и ниже, поскольку DDR4 использует другую безопасность и обычно может быть только прочитан. Можно использовать такой инструмент, как SPDTool или аналогичный, и заменить чип на тот, у которого есть свободная линия WP, чтобы его можно было изменить на месте. На некоторых чипсетах появляется сообщение "Несовместимый драйвер SMBus?" можно увидеть, поэтому чтение также запрещено.

Некоторое старое оборудование требует использования модулей SIMM с параллельным обнаружением присутствия (чаще называемое просто обнаружением присутствия или PD). Некоторое оборудование использует нестандартное кодирование PD, в частности компьютеры IBM и Hewlett-Packard LaserJet и другие принтеры.