Intel QuickPath Interconnect (QPI ) является двухточечным процессор межсоединение, разработанный Intel, который заменил фронтальную шину (FSB) в Xeon, Itanium и некоторые настольные платформы, начиная с 2008 года. Это увеличило масштабируемость и доступную пропускную способность. До объявления названия компания Intel называла его Common System Interface (CSI ). Более ранние версии были известны как еще один протокол (YAP) и YAP +.

QPI 1.1 - это значительно переработанная версия, представленная в Sandy Bridge-EP (Romley платформа).

QPI был заменен на Intel Ultra Path Interconnect (UPI) в процессорах Skylake -SP Xeon на базе разъема LGA 3647.

Хотя иногда его называют «шиной», QPI - это точка-точка -точка межсоединения. Он был разработан, чтобы конкурировать с HyperTransport, который использовался Advanced Micro Devices (AMD) примерно с 2003 года. Intel разработала QPI в своем Массачусетском Центре проектирования микропроцессоров (MMDC) членами того, что была Alpha Development Group, которую Intel приобрела у Compaq и HP и, в свою очередь, изначально была создана Digital Equipment Corporation (DEC). О его разработке было сообщено еще в 2004 году.

Intel впервые поставила его для настольных процессоров в ноябре 2008 года на Intel Core i7-9xx и X58 набор микросхем. Он был выпущен в процессорах Xeon под кодовым названием Nehalem в марте 2009 года и в процессорах Itanium в феврале 2010 года (кодовое имя Tukwila).

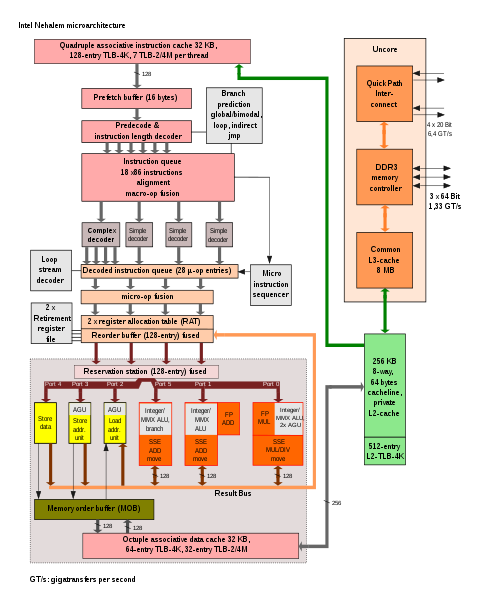

QPI - это uncore в микроархитектуре Intel Nehalem

QPI - это uncore в микроархитектуре Intel Nehalem QPI - это элемент системной архитектуры, которую Intel называет архитектурой QuickPath, которая реализует то, что Intel называет технологией QuickPath. В простейшей форме на однопроцессорной материнской плате один QPI используется для подключения процессора к концентратору ввода-вывода (например, для подключения Intel Core i7 к X58 ). В более сложных экземплярах архитектуры отдельные пары каналов QPI соединяют один или несколько процессоров и один или несколько концентраторов ввода-вывода или концентраторов маршрутизации в сети на материнской плате, позволяя всем компонентам получать доступ к другим компонентам через сеть. Как и в случае с HyperTransport, архитектура QuickPath предполагает, что в процессоры будут интегрированы контроллеры памяти, и обеспечивает архитектуру неравномерного доступа к памяти (NUMA).

Каждый QPI состоит из двух 20-полосных двухточечных каналов передачи данных, по одному в каждом направлении (полнодуплексный ), с отдельной парой тактовых импульсов в каждом направлении, всего 42 сигналы. Каждый сигнал представляет собой дифференциальную пару , поэтому общее количество выводов равно 84. 20 дорожек данных разделены на четыре «квадранта» по 5 дорожек в каждом. Базовая единица передачи - это 80-битный flit, который передается за два тактовых цикла (четыре 20-битных передачи, две за такт). 80-битный flit имеет 8 бит для обнаружения ошибок, 8 бит для «заголовка канального уровня» и 64 бита для данных. Пропускная способность QPI объявляется путем вычисления передачи 64 битов (8 байтов) данных каждые два тактовых цикла в каждом направлении.

Хотя первоначальные реализации используют одиночные четырехквадрантные ссылки, спецификация QPI допускает другие реализации. Каждый квадрант можно использовать независимо. На высоконадежных серверах канал QPI может работать в ухудшенном режиме. Если один или несколько из 20 + 1 сигналов выйдут из строя, интерфейс будет работать с оставшимися сигналами 10 + 1 или даже 5 + 1, даже переназначая часы на сигнал данных, если часы не работают. Первоначальная реализация Nehalem использовала полный четырехквадрантный интерфейс для достижения 25,6 ГБ / с, что обеспечивает вдвое большую теоретическую пропускную способность, чем у Intel 1600 МГц FSB, используемой в чипсете X48.

Хотя некоторые высокопроизводительные процессоры Core i7 имеют QPI, другие «массовые» настольные и мобильные процессоры Nehalem, предназначенные для однопроцессорных плат (например, LGA 1156 Core i3, Core i5 и другие Процессоры Core i7 из семейств Lynnfield / Clarksfield и последующих) не предоставляют QPI извне, поскольку эти процессоры не предназначены для участия в многопроцессорных системах. Однако QPI используется внутри этих микросхем для связи с «uncore », который является частью микросхемы, содержащей контроллеры памяти, PCI Express на стороне ЦП и графический процессор, если таковой имеется; ядро может находиться или не находиться на том же кристалле, что и ядро ЦП, например, оно находится на отдельном кристалле в Westmere -based Clarkdale / Arrandale. Эти однопроцессорные микросхемы, выпущенные после 2009 г., взаимодействуют извне через более медленные интерфейсы DMI и PCI Express, поскольку функции традиционного северного моста фактически интегрированы в эти процессоры, начиная с Lynnfield, Clarksfield., Кларкдейл и Аррандейл; таким образом, нет необходимости нести расходы на доступ к (бывшему) интерфейсу передней шины через сокет процессора. Хотя связь QPI между ядром и ядром отсутствует в настольных и мобильных процессорах Sandy Bridge (как, например, в Clarkdale), внутреннее кольцевое соединение между ядрами на кристалле также основано на принципах, лежащих в основе QPI, по крайней мере, что касается когерентности кэша.

QPI работает с тактовой частотой 2,4 ГГц, 2,93 ГГц, 3,2 ГГц, 3,6 ГГц, 4,0 ГГц или 4,8 ГГц (частоты 3,6 ГГц и 4,0 ГГц были введены с платформой Sandy Bridge-E / EP и 4,8 ГГц с платформой Haswell-E / EP). Тактовая частота для конкретного канала зависит от возможностей компонентов на каждом конце канала и характеристик сигнала пути прохождения сигнала на печатной плате. Неэкстремальные процессоры Core i7 9xx ограничены частотой 2,4 ГГц при штатных эталонных тактовых частотах. Передача битов происходит как по нарастающему, так и по спадающему фронту тактовой частоты, поэтому скорость передачи вдвое превышает тактовую частоту.

Intel описывает пропускную способность данных (в ГБ / с), считая только 64-битные полезные данные в каждом 80-битном флите. Однако затем Intel удваивает результат, потому что пара однонаправленных каналов передачи и приема может быть активна одновременно. Таким образом, Intel описывает пару каналов QPI с 20 полосами (отправка и получение) с тактовой частотой 3,2 ГГц как имеющую скорость передачи данных 25,6 ГБ / с. Тактовая частота 2,4 ГГц обеспечивает скорость передачи данных 19,2 ГБ / с. В более общем плане, по этому определению двухканальный 20-полосный QPI передает восемь байтов за такт, по четыре в каждом направлении.

Скорость вычисляется следующим образом:

QPI определяется как пятиуровневая архитектура с отдельными физическим, канальным, маршрутизационным, транспортным и протокольным уровнями. В устройствах, предназначенных только для использования QPI точка-точка без пересылки, таких как процессоры Core i7-9xx и Xeon DP, транспортный уровень отсутствует, а уровень маршрутизации минимален.