Intel D8255

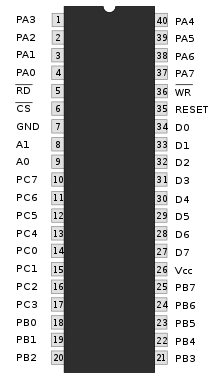

Intel D8255  Распиновка i8255

Распиновка i8255 Intel 8255 (или i8255 ) Программируемый Периферийный интерфейс (PPI) чип был разработан и изготовлен Intel в первой половине 1970-х годов для микропроцессора Intel 8080. 8255 имеет 24 параллельных входных / выходных линии с различными программируемыми режимами работы.

8255 является членом семейства MCS-85 микросхем, разработанных Intel для использования с микропроцессорами 8085 и 8086 и их потомки. Сначала он был доступен в 40-выводном корпусе DIP, а затем в 44-выводном корпусе PLCC. Он нашел широкое применение в системах цифровой обработки и позже был клонирован другими производителями. 82C55 - это версия CMOS, обеспечивающая более высокую скорость и меньшее потребление тока.

Функциональные возможности 8255 теперь в основном встроены в более крупные микросхемы обработки СБИС в качестве подфункции. CMOS версия 8255 все еще создается Renesas, но в основном используется для расширения ввода / вывода микроконтроллеров.

8255 имеет функцию, аналогичную MOS Technology 6522 (универсальный интерфейсный адаптер) и 6526 MOS Technology CIA (адаптер сложного интерфейса), оба разработаны для семейства 6502.

Все эти микросхемы изначально были доступны в 40-выводном корпусе DIL. 8255 имеет 24 используемых контакта ввода / вывода, тогда как микросхемы MOS имеют только 16 контактов ввода / вывода плюс 4 контакта управления. Однако микросхемы MOS содержат больше функций, таких как два программируемых таймера перезагрузки и простая функция регистра сдвига ввода / вывода. Кроме того, устройства MOS позволяют индивидуально программировать направление (вход или выход) всех их выводов ввода / вывода. Контакты ввода / вывода 8255 имеют только четыре программируемых бита направления: один для всего порта A (7: 0), один для порта B (7: 0), один для порта C (3: 0) и один для порта C ( 7: 4).

Другими сопоставимыми микропроцессорными микросхемами ввода / вывода являются программируемый периферийный интерфейс 2655 из семейства Signetics 2650, Motorola 6820 PIA (адаптер периферийного интерфейса) из Семейство Motorola 6800 и Western Design Center WDC 65C21.

Версия Intel ID8255A промышленного уровня была доступна по цене 17,55 долларов США в количестве 100 шт. вверх. Доступная версия Intel 8255A-5 стоила 6,55 долларов США при количестве 100 или более.

8255 широко использовался во многих микрокомпьютерных / микроконтроллерных системах и домашних компьютерах, например, SV-328 и все модели MSX. 8255 использовался в исходных IBM-PC, PC / XT, PC / jr и клонах, а также в многочисленных домашних компьютерах, таких как N8VEM.

8255 предоставляет ЦП или цифровой системе доступ к программируемым параллельным вводам / выводам. 8255 имеет 24 входа / выхода. Они разделены на три 8-битных порта (A, B, C). Порт A и порт B могут использоваться как 8-битные порты ввода / вывода. Порт C может использоваться как 8-битный порт ввода / вывода или как два 4-битных порта ввода / вывода или для выработки сигналов подтверждения для портов A и B.

Три порта далее сгруппированы следующим образом:

Доступно восемь линий данных (D0 – D7) (с 8-битный буфер данных) для чтения / записи данных в порты или регистр управления в состоянии

| A1 | A0 | Выбран порт |

|---|---|---|

| 0 | 0 | порт A |

| 0 | 1 | порт B |

| 1 | 0 | порт C |

| 1 | 1 | регистр управления |

Выбор микросхемы управляющего сигнала

Регистр управления (или логика управления, или регистр командного слова) - это 8-битный регистр, используемый для выбора режимов работы и обозначения ввода / вывода портов.

Существует два основных режима работы 8255:

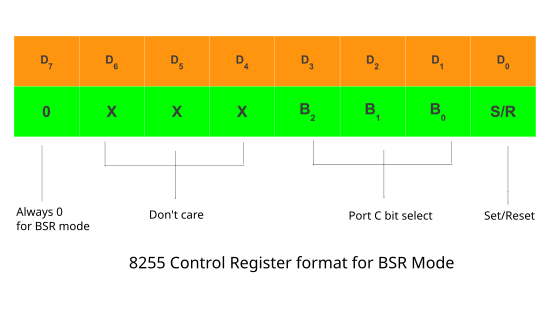

Два режима выбираются на основе значения, присутствующего в бите D 7 регистра управляющего слова. Когда D 7 = 1, 8255 работает в режиме ввода-вывода, а когда D 7 = 0, он работает в режиме BSR.

Режим установки / сброса битов (BSR) доступен только для порта C. Каждая строка порта C (ПК 7 - ПК 0) может быть установлена или сброшена путем записи подходящего значения в регистр управляющего слова. Режим BSR и режим ввода / вывода независимы, и выбор режима BSR не влияет на работу других портов в режиме ввода / вывода.

8255 Режим BSR

8255 Режим BSR Выбор вывода порта C определяется следующим образом:

| D3 | D2 | D1 | Выбран бит / вывод порта C. |

|---|---|---|---|

| 0 | 0 | 0 | PC0 |

| 0 | 0 | 1 | PC1 |

| 0 | 1 | 0 | PC2 |

| 0 | 1 | 1 | PC3 |

| 1 | 0 | 0 | PC4 |

| 1 | 0 | 1 | PC5 |

| 1 | 1 | 0 | PC6 |

| 1 | 1 | 1 | PC7 |

В качестве примера, если необходимо установить PC 5, то в управляющем слове

Таким образом, согласно приведенным выше значениям, 0B (шестнадцатеричный) будет загружен в регистр управляющего слова (CWR).

| D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 0 | 1 | 1 |

Этот режим выбирается, когда бит D 7 регистра управляющего слова равен 1. Существует три режима ввода / вывода:

Управляющее слово ввода / вывода Формат

Управляющее слово ввода / вывода Формат | D6 | D5 | Режим |

|---|---|---|

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | X | 2 |

Например, если порт B и верхний порт C должны быть инициализированы как входные порты, а нижний порт C и порт A в качестве портов вывода (все в режиме 0):

Следовательно, для желаемой операции регистр управляющего слова должен быть загружен с помощью "10001010" = 8A (шестнадцатеричный) .

В этом режиме порты могут использоваться для простого ввода-вывода. / O операции без сигналов подтверждения. Порт A, порт B обеспечивают простую операцию ввода-вывода. Две половины порта C могут использоваться либо вместе как дополнительный 8-битный порт, либо они могут использоваться как отдельные 4-битные порты. Поскольку две половины порта C независимы, их можно использовать так, что одна половина инициализируется как входной порт, а другая половина инициализируется как выходной порт.

Функции ввода / вывода в режиме 0 следующие:

«С фиксацией» означает, что биты помещаются в регистр хранения (массив триггеров), который содержит выходная константа, даже если входы изменяются после фиксации.

Выходы 8255 фиксируются для хранения последних записанных в них данных. Это необходимо, потому что данные остаются на шине только один цикл. Таким образом, без фиксации выходы станут недействительными, как только цикл записи завершится.

Входы не фиксируются, потому что ЦП должен только считывать их текущие значения, а затем сохранять данные в регистре ЦП или в памяти, если к ним нужно обратиться позже. Если вход изменяется во время чтения порта, результат может быть неопределенным.

CS низким. Затем он выбирает желаемый порт, используя строки A 0 и A 1.

CS низким. Затем он выбирает желаемый порт, используя строки A 0 и A 1. RD-сигнал для чтения данных с внешнего периферийного устройства через системную шину данных.

RD-сигнал для чтения данных с внешнего периферийного устройства через системную шину данных. CS низким. Затем он выбирает желаемый порт, используя строки A 0 и A 1.

CS низким. Затем он выбирает желаемый порт, используя строки A 0 и A 1. WR сигнал для записи данных в выбранный порт через системную шину данных. Эти данные затем принимаются внешним периферийным устройством, подключенным к выбранному порту.

WR сигнал для записи данных в выбранный порт через системную шину данных. Эти данные затем принимаются внешним периферийным устройством, подключенным к выбранному порту.Когда мы хотим использовать порт A или порт B для ввода квитирования (стробирования) или операции вывода, мы инициализируем этот порт в режиме 1 (порт A и порт B могут быть инициализированы для работы в разных режимах, то есть, например, порт A может работать в режиме 0, а порт B в режиме 1). Некоторые контакты порта C работают как линии подтверждения.

Для порта B в этом режиме (независимо от того, действует ли он как порт ввода или порт вывода), выводы PC0, PC1 и PC2 функционируют как линии подтверждения.

Если порт A инициализирован как входной порт режима 1, то PC3, PC4 и PC5 функционируют как сигналы подтверждения. Контакты PC6 и PC7 доступны для использования в качестве линий ввода / вывода.

Режим 1, который поддерживает квитирование, имеет следующие особенности:

Входные сигналы квитирования

Выходные сигналы установления связи

В этом режиме можно инициализировать только порт A. Порт A может использоваться для двунаправленной передачи данных подтверждения. Это означает, что данные могут вводиться или выводиться на одних и тех же восьми линиях (PA0 - PA7). Контакты PC3 - PC7 используются в качестве линий подтверждения для порта A. Остальные контакты порта C (PC0 - PC2) могут использоваться как линии ввода / вывода, если группа B инициализирована в режиме 0, или как квитирование для порта B, если группа B - инициализируется в режиме 1. В этом режиме 8255 может использоваться для расширения системной шины до подчиненного микропроцессора или для передачи байтов данных на контроллер гибких дисков и обратно. Сигналы подтверждения и квитирования предоставляются для поддержания надлежащего потока данных и синхронизации между передатчиком и приемником данных.