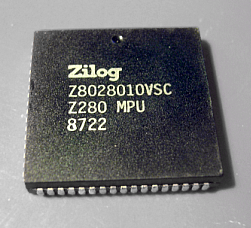

Z280 в пакете PLCC68

Z280 в пакете PLCC68  процессор STEbus Z280

процессор STEbus Z280 Zilog Z280 - это 16-битный микропроцессор, усовершенствованный вариант архитектуры Zilog Z80, представленный в июле 1987 года. В основном это Z800, переименованный, с небольшими улучшениями, такими как производство в КМОП. Это был коммерческий провал. Zilog добавил блок управления памятью (MMU), чтобы расширить диапазон адресов до 16 МБ, функции для многозадачности и многопроцессорности. Конфигурации и сопроцессора и 256 байтов статической ОЗУ на кристалле, конфигурируемые либо как кэш для инструкций и / или данных, либо как часть обычного адресного пространства. Он имеет огромное количество новых инструкций и режимов адресации, что дает в общей сложности более 2000 комбинаций. Он способен эффективно обрабатывать 32-битные операции с данными, включая аппаратное умножение, деление и знаковое расширение. Он предлагает режимы работы супервизора и пользователя, а также дополнительно разделяет адресные пространства для инструкций и данных в обоих режимах (всего четыре возможных адресных пространства). Его внутренний тактовый сигнал может быть настроен для работы с частотой в 1, 2 или 4 раза превышающей внешнюю тактовую частоту (например, 12 МГц CPU с 3 МГц автобус ). В отличие от Z80, Z280 использует мультиплексную схему для шин адреса и данных. Более успешные расширения архитектуры Z80 включают Hitachi HD64180 в 1986 году и Zilog eZ80 в 2001 году. См. Далее Zilog Z800.

Z280 для своего времени обладал множеством расширенных функций, большинство из которых никогда больше не использовалось процессором Zilog:

Эта статья основана на материалах, взятых из Free On-line Dictionary of Computing до 1 ноября 2008 г. и включенных в соответствии с условиями «перелицензирования» GFDL, версия 1.3 или новее.

.