| INPUT | OUTPUT | |

| A | B | A XOR B |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

CMOS XOR gate

CMOS XOR gate XOR gate (иногда EOR или EXOR и произносится как Exclusive OR ) - это цифровой логический элемент , который дает истинное значение (1 или HIGH), когда количество истинных входов нечетное. Шлюз XOR реализует исключающее ИЛИ ; то есть, истинный результат получается, если один и только один из входов в вентиль истинен. Если оба входа ложны (0 / LOW) или оба верны, результат будет ложным. XOR представляет функцию неравенства, то есть выход истинен, если входы не похожи, в противном случае выход ложный. Способ запомнить XOR - это «должен быть один или другой, но не оба».

XOR также можно рассматривать как сложение по модулю 2. В результате вентили XOR используются для реализации двоичного сложения в компьютерах. Полусумматор состоит из логического элемента XOR и логического элемента И. Другие применения включают вычитатели, компараторы и управляемые инверторы.

алгебраические выражения

Есть три схематических символа для вентилей XOR: традиционный ANSI и символы DIN и символ IEC. В некоторых случаях символ DIN используется с ⊕ вместо ≢. Для получения дополнительной информации см. Символы логических вентилей.

|  |  | ||

| Схематическое обозначение ANSI XOR | Схематическое обозначение DIN XOR | Схематическое обозначение IEC XOR |

Логические символы ⊕, Jpq, а ⊻ может использоваться для обозначения операции XOR в алгебраических выражениях.

C-подобные языки используют символ вставки ^ для обозначения побитового XOR. (Обратите внимание, что каретка не обозначает логическое соединение (AND) в этих языках, несмотря на схожесть символов.)

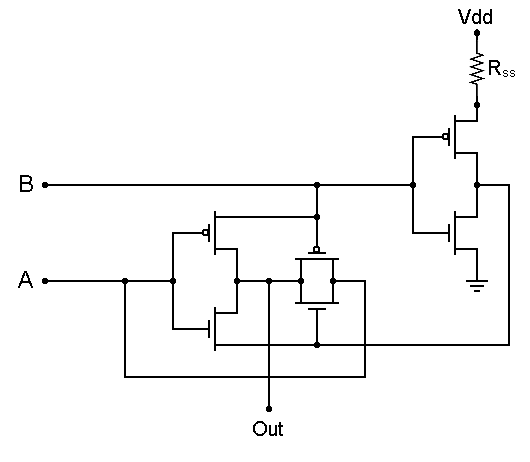

XOR ворота могут быть построены с использованием полевых МОП-транзисторов. Вот схема логики проходного транзистора реализации логического элемента XOR.

Передаточный вентиль Логическая разводка логического элемента XOR

Передаточный вентиль Логическая разводка логического элемента XOR Примечание. Резистор «Rss» предотвращает шунтирование тока непосредственно от «A» и «B» на выходе. Без него, если схема, которая обеспечивает входы A и B, не имеет надлежащей управляемой способности, выход может не качаться от рельса к рельсу или сильно ограничен по скорости нарастания. Резистор «Rss» также ограничивает ток от Vdd до земли, что защищает транзисторы и экономит энергию при переходе транзисторов между состояниями.

Схема логического элемента XOR с использованием трех смешанных вентилей

Схема логического элемента XOR с использованием трех смешанных вентилей Если вентиль определенного типа недоступен, схема, реализующая ту же функцию, может быть построена из других доступных вентилей. Схема, реализующая функцию XOR, может быть тривиально построена из элемента XNOR, за которым следует элемент NOT. Если мы рассмотрим выражение

В качестве альтернативы, если доступны разные вентили, мы можем применить булеву алгебру для преобразования

Схема логического элемента XOR может быть создана из четырех элементов NAND. Фактически, вентили И-НЕ и ИЛИ-ИЛИ являются так называемыми «универсальными вентилями», и любая логическая функция может быть построена только на основе логики И-НЕ или логики ИЛИ-НЕ. Если четыре логических элемента И-НЕ заменяются на вентили ИЛИ-ИЛИ, это приводит к логическому элементу ИСКЛЮЧАЮЩЕЕ ИЛИ, который может быть преобразован в элемент ИЛИ-ИЛИ. путем инвертирования выхода или одного из входов (например, с помощью пятого элемента ИЛИ-НЕ ).

| Требуемый вентиль | Конструкция И-НЕ | Конструкция ИЛИ-НЕ |

|---|---|---|

|  |  |

Альтернативная конфигурация состоит из пяти элементов ИЛИ-НЕ в топологии, которая подчеркивает построение функции из

| Требуемый вентиль | Конструкция И-НЕ | Конструкция ИЛИ-ИЛИ |

|---|---|---|

|  |  |

Для конструкций И-НЕ верхнее расположение требует меньшего количества вентилей. Для конструкций NOR нижнее расположение предлагает преимущество более короткой задержки распространения (временная задержка между изменением входа и изменением выхода).

Буквальная интерпретация имени «исключающее ИЛИ» или наблюдение за прямоугольным символом IEC поднимает вопрос о правильном поведении с дополнительными входами. Если бы логический вентиль принимал три или более входных сигнала и выдавал истинный выход, если бы ровно один из этих входов был истинным, то это фактически был бы детектор one-hot (и это действительно так для всего два входа). Однако на практике это редко реализуется.

Обычно последующие входы применяются как каскад двоичных операций исключающее ИЛИ: первые два сигнала подаются в логический элемент XOR, затем выход этого элемента подается во второй элемент XOR. затвор вместе с третьим сигналом и так далее для всех оставшихся сигналов. В результате получается схема, которая выводит 1, когда количество единиц на ее входах нечетно, и 0, когда количество входящих единиц четно. Это делает его практически полезным в качестве генератора четности или сумматора по модулю 2 .

. Например, микрочип 74LVC1G386 рекламируется как логический вентиль с тремя входами, и реализует генератор четности.

Пример принципиальной схемы полусумматора

Пример принципиальной схемы полусумматора  Пример принципиальной схемы полного сумматора

Пример принципиальной схемы полного сумматора Логический вентиль XOR можно использовать как единицу -bit сумматор, который складывает любые два бита для вывода одного бита. Например, если мы добавим 1 плюс 1 в двоичный, мы ожидаем двухбитного ответа, 10 (т.е. 2 в десятичной системе счисления). Поскольку завершающий бит суммы в этом выходе достигается с помощью XOR, предыдущий бит переноса вычисляется с помощью логического элемента И. Это основной принцип в полусумматорах. Цепь полного сумматора немного большего размера может быть объединена в цепочку для добавления более длинных двоичных чисел.

Генераторы псевдослучайных чисел (PRN), в частности регистры сдвига с линейной обратной связью, определяются в терминах операция исключающее ИЛИ. Следовательно, подходящая установка логических элементов XOR может моделировать регистр сдвига с линейной обратной связью для генерации случайных чисел.

вентили XOR выдают 0, когда оба входа совпадают. При поиске определенного битового шаблона или последовательности PRN в очень длинной последовательности данных можно использовать серию вентилей XOR для параллельного сравнения строки битов из последовательности данных с целевой последовательностью. Затем можно подсчитать количество 0 выходов, чтобы определить, насколько хорошо последовательность данных соответствует целевой последовательности. Корреляторы используются во многих устройствах связи, таких как приемники и декодеры CDMA для исправления ошибок и кодов каналов. В приемнике CDMA корреляторы используются для извлечения полярности конкретной последовательности PRN из объединенного набора последовательностей PRN.

Коррелятор, ищущий 11010 в последовательности данных 1110100101, будет сравнивать входящие биты данных с целевой последовательностью при каждом возможном смещении, подсчитывая количество совпадений (нулей):

1110100101 (данные) 11010 (цель) 00111 (XOR) 2 нулевых бита 1110100101 11010 00000 5 нулевых битов 1110100101 11010 01110 2 нулевых бита 1110100101 11010 10011 2 нулевых бита 1110100101 11010 01000 4 нулевых бита 1110100101 11010 11111 0 нулевых битов Соответствует смещению:. ::::::: ----------- 0 1 2 3 4 5

В этом примере наилучшее совпадение происходит, когда целевая последовательность смещена на 1 бит и все пять бит совпадают. При смещении на 5 бит последовательность в точности совпадает с обратной. Глядя на разницу между количеством единиц и нулей, которые выходят из банка вентилей XOR, легко увидеть, где происходит последовательность и инвертирована она или нет. Более длинные последовательности легче обнаружить, чем короткие.

| Викискладе есть носители, связанные с вентилями XOR. |