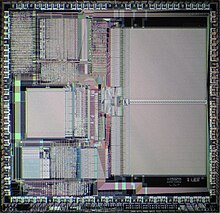

Intergraph Clipper C4 (C400) CPU

Intergraph Clipper C4 (C400) CPU Архитектура Clipper - это 32-битная RISC -подобная архитектура набора команд, разработанная Fairchild Semiconductor. Эта архитектура никогда не пользовалась большим успехом на рынке, и единственными производителями компьютеров, которые создали основные линейки продуктов с использованием процессоров Clipper, были Intergraph и High Level Hardware. Первые процессоры, использующие архитектуру Clipper, были разработаны и проданы Fairchild, но ответственное за них подразделение впоследствии было продано Intergraph в 1987 году; Intergraph продолжил работу над процессорами Clipper для использования в своих собственных системах.

В архитектуре Clipper использовался упрощенный набор инструкций по сравнению с более ранними архитектурами CISC, но она действительно включала некоторые более сложные инструкции, чем были в других современных процессорах RISC. Эти инструкции были реализованы в так называемой макрокоманде ROM в ЦП клиппера. Эта схема позволяла Clipper иметь несколько более высокую плотность кода , чем другие процессоры RISC.

Матрица ЦП Clipper C100

Матрица ЦП Clipper C100  Матрица ЦП Clipper C300

Матрица ЦП Clipper C300 Первым микропроцессором Clipper, произведенным Fairchild, был C100, который стал доступен в 1986 году. За ним последовал более быстрый C300 от Intergraph в 1988 году. Последней моделью Clipper был C400, выпущенный в 1990 году., который был значительно переработан, чтобы работать быстрее, и добавлено больше регистров с плавающей запятой. Процессор C400 объединил два ключевых архитектурных метода для достижения нового уровня производительности - суперскалярная диспетчеризация инструкций и суперпайплайн операции.

В то время как многие процессоры того времени использовали либо суперскалярную отправку инструкций, либо суперпайплайновую операцию, Clipper C400 был первым процессором, который использовал оба.

Intergraph начал работу над последующим проектом процессора Clipper, известным как C5, но он так и не был завершен и выпущен. Тем не менее, для C5 были разработаны некоторые передовые технологии проектирования процессоров, и Intergraph получила на них патенты. Эти патенты, наряду с оригинальными патентами Clipper, послужили основанием для исков Intergraph о нарушении патентных прав против Intel и других компаний.

Die Clipper C300 CAMMU

Die Clipper C300 CAMMU В отличие от многих других микропроцессоры, процессоры Clipper фактически представляли собой наборы из нескольких отдельных микросхем. C100 и C300 состоят из трех микросхем: одного центрального процессора, содержащего как целочисленный блок, так и блок с плавающей запятой, и два блока кеша и управления памятью ( CAMMU), один отвечает за данные, а другой за инструкции. Модули CAMMU содержали кеши, буферы резервного преобразования и поддержку защиты памяти и виртуальной памяти. C400 состоит из четырех основных блоков: целочисленного ЦП, FPU, MMU и блока кэш-памяти. Первоначальная версия использовала по одной микросхеме для ЦП и FPU и дискретные элементы для MMU и блока кэш-памяти, но в более поздних версиях MMU и блок кэширования были объединены в одну микросхему CAMMU.

У Clipper было 16 целочисленных регистров (R15 использовался как указатель стека), 16 регистров с плавающей запятой (ограничено 8 в ранних реализациях), плюс счетчик программ ( PC), слово состояния процессора (PSW), содержащее флаги состояния ALU и FPU и разрешения прерывания, и слово состояния системы (SSW), содержащее разрешение внешнего прерывания, режим пользователя / супервизора и биты управления трансляцией адресов.

Режим пользователя и режим супервизора имели отдельные банки целочисленных регистров. Обработка прерываний заключалась в сохранении ПК, PSW и SSW в стеке, очистке PSW и загрузке ПК и SSW из вектора ловушки памяти.

Ограничитель был архитектурой загрузки / сохранения, где арифметические операции могли указывать только регистр или непосредственные операнды. Базовая инструкция «посылка» состояла из 16 бит: 8 бит кода операции, 4 бита исходного регистра и 4 бита регистра назначения. Формы с непосредственным операндом позволили 1 или 2 следующим пакетам инструкций указать 16-битный (расширенный по знаку) или 32-битный непосредственный операнд. Процессор всегда был прямым порядком байтов, включая непосредственные операнды.

Специальная «быстрая» кодировка с 4-битным беззнаковым операндом была предоставлена для добавления, вычитания, загрузки (быстрое перемещение для регистрации), а не (перемещение дополнения для быстрой регистрации).

Режимы адресации для инструкций загрузки / сохранения и перехода были следующими. Все смещения были обозначены знаком.

Помимо обычных логических и арифметических операций, процессор поддерживал:

Допускаются более сложные макрокоманды:

Большинство инструкций допускают ar Необходимо указать регистр указателя битового стека, но, за исключением сохранения / восстановления пользовательского регистра, операции с несколькими регистрами могут использовать только R15.

Фотография рабочей станции Intergraph CLIX

Фотография рабочей станции Intergraph CLIX Intergraph продала несколько поколений систем Clipper, в том числе серверы и рабочие станции. Эти системы включали линейки продуктов InterAct, InterServe и InterPro и были ориентированы в основном на рынок CAD.

Fairchild продвигал операционную систему, версию UNIX System V, для использования с Clipper. Intergraph принял CLIX для своих систем на базе Clipper и продолжил его развитие; это была единственная операционная система, доступная для этих систем. Intergraph действительно работал над версией Microsoft Windows NT для систем Clipper и публично продемонстрировал ее, но эти усилия были отменены перед выпуском. Intergraph решил прекратить выпуск линейки Clipper и вместо этого начал продавать системы x86 с Windows NT.