Четырехфазная логика - это тип и методология разработки для динамической логики. Это позволило инженерам-неспециалистам разрабатывать довольно сложные ИС, используя процессы PMOS или NMOS. Он использует своего рода 4-фазный тактовый сигнал.

Р. К. «Боб» Бухер, инженер в Autonetics, изобрел четырехфазную логику и сообщил об этой идее Фрэнку Ванлассу в Fairchild Semiconductor ; Ванласс продвигал эту логическую форму в General Instrument Microelectronics Division. В феврале 1966 года Бухер изготовил первый рабочий четырехфазный чип, Autonetics DDA-интегратор ; Позже он разработал несколько микросхем для бортового компьютера Autonetics D200, используя эту технику.

В апреле 1967 года Джоэл Карп и Элизабет де Атли опубликовали статью «Используйте четырехфазную логику МОП-микросхемы. »в журнале« Электронный дизайн ». В том же году Коэн, Рубинштейн и Ванласс опубликовали «Четырехфазные тактовые системы MTOS». Ванласс был директором по исследованиям и разработкам в General Instrument Microelectronics Division в Нью-Йорке с тех пор, как покинул Fairchild Semiconductor в 1964 году.

Ли Бойсел, ученик Ванласса и дизайнер в Fairchild Компания Semiconductor, позже основавшая Four-Phase Systems, в октябре 1967 г. на встрече International Electron Devices выступила с докладом "в последних новостях" о четырехфазном 8-битном сумматоре. Дж. Л. Сили, менеджер отдела MOS-операций в General Instrument Microelectronics Division, также писал о четырехфазной логике в конце 1967 года.

В 1968 году Бойсел опубликовал статью «Сумматор на микросхеме: LSI помогает снизить стоимость небольших машин». в журнале «Электроника»; В том же году появляются четырехэтапные документы Я. Т. Йена. Вскоре последовали и другие статьи.

Бойсел вспоминает, что четырехфазная динамическая логика позволила ему достичь 10-кратной плотности упаковки, 10-кратной скорости и 1/10 мощности по сравнению с другими методами МОП, которые использовались в то время ( металлический вентиль насыщенная нагрузка логика PMOS ), используя процесс MOS первого поколения в Fairchild.

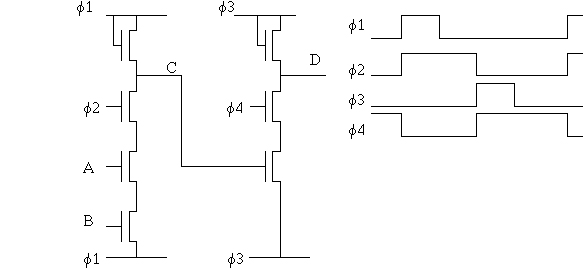

В основном есть два типа логического элемента - элемент «1» и элемент «3». Они отличаются только фазами тактового сигнала, используемыми для их управления. У ворот может быть любая логическая функция; таким образом, потенциально все ворота имеют индивидуальную планировку. Пример 2-входного затвора NAND 1 и затвора инвертора 3 вместе с их фазами тактовой частоты (в примере используются транзисторы NMOS) показаны ниже:

Тактовые импульсы ϕ1 и ϕ3 не должны перекрываться, как и ϕ2. и ϕ4 тактов. Принимая во внимание вентиль 1, в течение максимального времени тактового сигнала ϕ1 (также известного как время предварительной зарядки ) выход C предварительно заряжается до V (ϕ1) −V th, где V th представляет пороговое значение транзистора предварительного заряда. В течение следующей четверти тактового цикла (время выборка ), когда ϕ1 низкий, а ϕ2 высокий, C либо остается на высоком уровне (если A или B низкие), либо C разряжается на низком уровне (если A и B высоко).

Входы A и B должны быть стабильными в течение этого времени выборки. Выход C становится действительным в течение этого времени - и поэтому выход с 1 вентилем не может управлять входами с 1 вентилем. Следовательно, 1 ворота должны кормить 3 ворот, а они, в свою очередь, должны кормить 1 ворота.

Еще одна вещь пригодится - 2 и 4 калитки. 2 строба подзаряжаются на ϕ1 и выборки на ϕ3:

, а 4 строба подзаряжаются на ϕ3 и отсчеты на ϕ1.

Правила соединения ворот следующие: 1 ворота могут управлять 2 воротами и / или 3 воротами; 2 ворот могут управлять только 3 воротами, 3 ворот могут управлять 4 воротами и / или 1 воротами, 4 ворот могут управлять только 1 воротами:

Четырехфазная логика работает хорошо; в частности, нет никаких опасностей гонки, потому что каждый элемент комбинационной логики включает регистр. Стоит отметить, что разводка не требует подключения каких-либо блоков питания - только тактовые линии. Кроме того, поскольку метод проектирования является безразмерным (см. Статическую логику), во многих конструкциях можно использовать транзисторы минимального размера.

Есть некоторые трудности:

С появлением CMOS Транзистор предварительной зарядки может быть заменен на дополнение к типу логического транзистора, что позволяет выходу затвора быстро заряжаться вплоть до высокого уровня тактовой линии, тем самым улучшая скорость, размах сигнала, потребляемую мощность и запас шума. Этот метод используется в логике домино.