| |

| Общая информация | |

|---|---|

| Запущен | 2010 |

| Снято с производства | 2020 |

| Производительность | |

| Макс. CPU тактовая частота | от 1,053 до 1,7 ГГц |

| кэш | |

| L1 кэш | 32 КБ на ядро |

| кэш L2 | 512 КБ на ядро |

| Архитектура и классификация | |

| Архитектура | x86-64 |

| Расширения | |

| Физические характеристики | |

| Транзисторы | |

| Ядра |

|

| Разъем (ы) |

|

| Продукты, модели, варианты | |

| Торговые марки | |

Xeon Phi - это серия x86 многоядерных процессоров, разработанных и изготовленных Intel. Он предназначен для использования в суперкомпьютерах, серверах и высокопроизводительных рабочих станциях. Его архитектура позволяет использовать стандартные языки программирования и интерфейсы прикладного программирования (API), такие как OpenMP.

Поскольку изначально он был основан на более ранней конструкции графического процессора (под кодовым названием «Larrabee» ) Intel, которая была отменена в 2009 году, он разделяет области приложений с графическими процессорами. Основное различие между Xeon Phi и GPGPU как Nvidia Tesla заключается в том, что Xeon Phi с x86-совместимым ядром может с меньшими изменениями запускать программное обеспечение, которое изначально предназначалось для стандартный процессор x86. Он был снят с производства из-за отсутствия спроса и проблем Intel с его 10-нм узлом.

Первоначально в виде дополнительных карт на базе PCIe, продукта второго поколения под кодовым названием Knights Landing было объявлено в июне 2013 года. Эти чипы второго поколения можно было использовать как автономный процессор, а не просто как дополнительную карту.

Суперкомпьютер Tianhe-2 использует процессоры Xeon Phi.

Суперкомпьютер Tianhe-2 использует процессоры Xeon Phi. В июне 2013 года суперкомпьютер Tianhe-2 в Национальном суперкомпьютерном центре в Гуанчжоу (NSCC-GZ) был объявлен самым быстрым суперкомпьютером в мире (по состоянию на июнь 2018 года он занимает 4-е место). В нем использовались сопроцессоры Intel Xeon Phi и процессоры Ivy Bridge -EP Xeon для достижения 33,86 петафлопс.

Линия продуктов Xeon Phi напрямую конкурировала с Nvidia Линии Tesla и AMD Radeon Instinct для глубокого обучения и карт GPGPU.

| Кодовое название | Технология | Комментарии |

|---|---|---|

| Knights Ferry | 45 нм | предлагается как карта PCIe; получено из проекта Larrabee |

| Knights Corner | 22 нм | , полученного из P54C; блок векторной обработки; первое устройство, которое будет объявлено как Xeon Phi |

| Knights Landing | 14 нм | , полученное от Silvermont / Airmont (Intel Atom); AVX-512 |

| Knights Mill | 14 нм | почти идентичен Knights Landing, но оптимизирован для глубокого обучения |

| Knights Hill | 10 нм | отменено |

Микроархитектура Larrabee (в разработке с 2006 г.) представила очень широкие (512-битные) блоки SIMD в x86 архитектура процессора, расширенная до когерентной кэш-памяти многопроцессорной системы, подключенной через кольцевую шину к памяти; каждое ядро было способно к четырехсторонней многопоточности. Из-за того, что дизайн предназначен для использования с графическим процессором, а также для вычислений общего назначения, чипы Larrabee также включают специализированное оборудование для выборки текстур. Проект по производству графического процессора для розничной продажи непосредственно из исследовательского проекта Larrabee был прекращен в мае 2010 года.

Еще одним современным исследовательским проектом Intel, реализующим архитектуру x86 на многоядерном процессоре, было «Одночиповое облако. Компьютер '(прототип представлен в 2009 г.), дизайн, имитирующий компьютерный центр обработки данных с облачными вычислениями на одном кристалле с несколькими независимыми ядрами: прототип конструкции включал 48 ядер на чип с аппаратной поддержкой выборочной частоты и напряжения. управление ядрами для максимального повышения энергоэффективности и включение ячеистой сети для обмена сообщениями между чипами. В дизайне не хватало ядер, согласованных с кешем, и он был сосредоточен на принципах, которые позволили бы масштабировать проект до гораздо большего числа ядер.

Teraflops Research Chip (прототип представлен в 2007 году) - экспериментальный 80-ядерный чип с двумя модулями с плавающей запятой на ядро, реализующий 96-битную архитектуру VLIW вместо архитектуры x86. В рамках проекта были исследованы методы межъядерной связи, управление питанием на каждом кристалле, и достигнут результат 1,01 TFLOPS на частоте 3,16 ГГц при потреблении энергии 62 Вт.

Многие интегрированные ядра Intel (MIC) прототип платы Knights Ferry, включающий процессор под кодовым названием Aubrey Isle, был объявлен 31 мая 2010 года. Было заявлено, что продукт является производным от проекта Larrabee и других исследований Intel, включая одночиповый облачный компьютер.

Продукт для разработки предлагался в виде карты PCIe с 32 упорядоченными ядрами с частотой до 1,2 ГГц с четырьмя потоками на ядро, 2 ГБ памяти GDDR5 и 8 МБ когерентной кеш-памяти L2 (256 КБ на ядро с 32 КБ кэш-памяти L1), и потребляемая мощность ~ 300 Вт, построенная по техпроцессу 45 нм. В ядре Aubrey Isle 1024-битная кольцевая шина (512-битная двунаправленная) соединяет процессоры с основной памятью. Одноплатная производительность превысила 750 GFLOPS. Платы-прототипы поддерживают только инструкции с плавающей запятой одинарной точности.

Первоначальные разработчики включали ЦЕРН, Корейский институт науки и технической информации ( КИСТИ) и суперкомпьютерный центр им. Лейбница. В число поставщиков оборудования для прототипов плат входили IBM, SGI, HP, Dell и другие.

Линия продуктов Knights Corner производится с размером процесса 22 нм с использованием Intel Tri -gate с более чем 50 ядрами на чип, и это первый многоядерный коммерческий продукт Intel.

В июне 2011 года SGI объявила о партнерстве с Intel для использования MIC архитектура в своих высокопроизводительных вычислительных продуктах. В сентябре 2011 года было объявлено, что Texas Advanced Computing Center (TACC) будет использовать карты Knights Corner в своем суперкомпьютере Stampede на 10 петафлопс, обеспечивая 8 петафлопс вычислительной мощности. Согласно "Stampede: Комплексная петафлопсная вычислительная среда", MIC второго поколения Intel (Knights Landing) будут добавлены, когда они станут доступны, увеличивая совокупную пиковую производительность Stampede как минимум до 15 петафлопс. "

15 В ноябре 2011 года Intel представила первую силиконовую версию процессора Knights Corner.

5 июня 2012 года Intel выпустила программное обеспечение с открытым исходным кодом и документацию по Knights Corner.

18 июня 2012 года Intel объявила на Гамбургской Международной конференции по суперкомпьютерам в 2012 году было сказано, что Xeon Phi будет торговой маркой, используемой для всех продуктов, основанных на их архитектуре с множеством интегрированных ядер. В июне 2012 года Cray объявила, что предложит 22-нм чипы Knight's Corner (под брендом Xeon Phi) в качестве сопроцессора в своих системах Cascade.

В В июне 2012 года ScaleMP объявил об обновлении виртуализации, позволяющем Xeon Phi использовать в качестве прозрачного расширения процессора, позволяя выполнять устаревший код MMX / SSE без изменений кода. Важным компонентом ядра сопроцессора Intel Xeon Phi является его векторный процессор (VPU). VPU имеет новый 512-битный набор инструкций SIMD, официально известный как Intel Initial Many Core Instructions (Intel IMCI). Таким образом, VPU может выполнять 16 операций с одинарной точностью (SP) или 8 с двойной точностью (DP) за цикл. VPU также поддерживает инструкции Fused Multiply-Add (FMA) и, следовательно, может выполнять 32 SP или 16 DP операций с плавающей запятой за цикл. Он также поддерживает целые числа. VPU также имеет расширенный математический модуль (EMU), который может выполнять такие операции, как обратное вычисление, извлечение квадратного корня и логарифм, что позволяет выполнять эти операции в векторном режиме с высокой пропускной способностью. EMU работает, вычисляя полиномиальные приближения этих функций.

12 ноября 2012 года Intel анонсировала два семейства сопроцессоров Xeon Phi, использующих размер процесса 22 нм: Xeon Phi 3100 и Xeon Phi 5110P. Xeon Phi 3100 будет способен выполнять более 1 терафлопс двойной точности инструкций с плавающей запятой с пропускной способностью памяти 240 ГБ / с при мощности 300 Вт. Xeon Phi 5110P будет способен выполнять 1,01 терафлопс при двойной точности. прецизионные инструкции с плавающей запятой с пропускной способностью памяти 320 ГБ / с при мощности 225 Вт. Xeon Phi 7120P будет способен выполнять 1,2 терафлопс инструкций с плавающей запятой двойной точности с пропускной способностью памяти 352 ГБ / с при 300 Вт.

17 июня 2013 года суперкомпьютер Tianhe-2 был объявлен TOP500 самым быстрым в мире. Tianhe-2 использовал процессоры Intel Ivy Bridge Xeon и Xeon Phi для достижения 33,86 петафлопс. Он был самым быстрым в списке за два с половиной года, последний раз в ноябре 2015 года.

Ядра Knights Corner основаны на модифицированной версии P54C. конструкция, использованная в оригинальном Pentium. В основе архитектуры Intel MIC лежит использование наследия x86 путем создания x86-совместимой многопроцессорной архитектуры, которая может использовать существующие программные инструменты распараллеливания. Инструменты программирования включают OpenMP, OpenCL, Cilk / Cilk Plus и специализированные версии Intel Fortran, C ++ и математические библиотеки.

Элементы дизайна, унаследованные от проекта Larrabee, включают x86 ISA, 4-процессорный SMT на ядро, 512-битные блоки SIMD, 32 КБ кэша инструкций L1, 32 КБ кэша данных L1, когерентный кэш L2 (512 КБ на ядро) и сверхширокую кольцевую шину, соединяющую процессоры и память.

512-битные инструкции SIMD Knights Corner разделяют многие внутренние функции с расширением AVX-512. Документация по набору команд доступна у Intel под названием расширения KNC.

| Имя | Серийный код | Ядра. (Потоки = 4 ядра). | Тактовая частота (МГц) | L2. Кэш | Память GDDR5 ECC | Пиковая DP. Вычисления. (GFLOPS) | TDP. (Вт) | Охлаждение. Система | Форм-фактор | Выпущено | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Базовое | Турбо | Количество | каналов | BW. ГБ / с | |||||||||

| Xeon Phi 3110X | SE3110X | 061 (244) | 1053 | - | 30,5 МБ | 06 ГБ | 12 | 240 | 1028 | 300 | Пустая плата | PCIe 2.0 x16 карта | ноябрь 2012 г. |

| 08 ГБ | 16 | 320 | |||||||||||

| Xeon Phi 3120A | SC3120A | 057 ( 228) | 1100 | - | 28,5 МБ | 06 ГБ | 12 | 240 | 1003 | 300 | Вентилятор / радиатор | 17 июня 2013 г. | |

| Xeon Phi 3120P | SC3120P | 057 (228) | 1100 | - | 28,5 МБ | 06 ГБ | 12 | 240 | 10 03 | 300 | Пассивный радиатор | 17 июня 2013 г. | |

| Xeon Phi 31S1P | BC31S1P | 057 (228) | 1100 | - | 28,5 МБ | 08 ГБ | 16 | 320 | 1003 | 270 | Пассивный радиатор | 17 июня 2013 | |

| Xeon Phi 5110P | SC5110P | 060 (240) | 1053 | - | 30,0 МБ | 08 ГБ | 16 | 320 | 1011 | 225 | Пассивный радиатор | 12 ноя 2012 | |

| Xeon Phi 5120D | SC5120D | 060 (240) | 1053 | - | 30,0 МБ | 08 ГБ | 16 | 352 | 1011 | 245 | Пустая плата | 230-контактная карта SFF | 17 июня 2013 г. |

| BC5120D | |||||||||||||

| Xeon Phi SE10P | SE10P | 061 (244) | 1100 | - | 30,5 МБ | 08 ГБ | 16 | 352 | 1074 | 300 | Пассивный радиатор | Карта PCIe 2.0 x16 | 12 Ноябрь 2012 |

| Xeon Phi SE10X | SE10X | 061 (244) | 1100 | - | 30,5 МБ | 08 ГБ | 16 | 352 | 107 4 | 300 | Чистая плата | 12 ноября 2012 г. | |

| Xeon Phi 7110P | SC7110P | 061 (244) | 1100 | 1250 | 30,5 МБ | 16 ГБ | 16 | 352 | 1220 | 300 | Пассивный радиатор | ??? | |

| Xeon Phi 7110X | SC7110X | 061 (244) | 1250 | ??? | 30,5 МБ | 16 ГБ | 16 | 352 | 1220 | 300 | Голая доска | ??? | |

| Xeon Phi 7120A | SC7120A | 061 (244) | 1238 | 1333 | 30,5 МБ | 16 ГБ | 16 | 352 | 1208 | 300 | Вентилятор / радиатор | 6 апреля 2014 г. | |

| Xeon Phi 7120D | SC7120D | 061 (244) | 1238 | 1333 | 30,5 МБ | 16 ГБ | 16 | 352 | 1208 | 270 | Пустая плата | SFF 230-контактная карта | март ??, 2014 г. |

| Xeon Phi 7120P | SC7120P | 061 (244) | 1238 | 1333 | 30,5 МБ | 16 ГБ | 16 | 352 | 1208 | 300 | Пассивный радиатор | Карта PCIe 2.0 x16 | 17 июня 2013 г. |

| Xeon Phi 7120X | SC7120X | 061 (244) | 1238 | 1333 | 30,5 МБ | 16 ГБ | 16 | 352 | 1208 | 300 | Голая плата | 17 июня 2013 г. | |

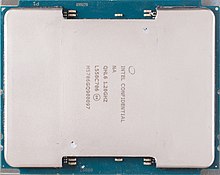

Intel Xeon Phi Knights Landing процессор

Intel Xeon Phi Knights Landing процессор  Тот же процессор, без маркировки

Тот же процессор, без маркировки  Die shot

Die shot Кодовое название для вторые поколения на архитектуре MIC от Intel. Корпорация Intel официально впервые раскрыла подробности о своих продуктах Intel Xeon Phi второго поколения 17 июня 2013 года. Intel заявила, что следующее поколение продуктов на базе архитектуры Intel MIC будет доступно в двух формах: сопроцессор или центральный процессор (ЦП), и производиться с использованием техпроцесса Intel 14 нм. Продукты Knights Landing будут включать встроенную память для значительно более высокой пропускной способности памяти.

Knights Landing содержит до 72 ядер Airmont (Atom) с четырьмя потоками на ядро, используя сокет LGA 3647, поддерживающий до 384 ГБ "дальнего" DDR4 2133 ОЗУ и 8–16 ГБ стека «около» 3D MCDRAM, версии куба гибридной памяти. Каждое ядро имеет два 512-битных векторных блока и поддерживает инструкции SIMD AVX-512, в частности, основные инструкции Intel AVX-512 (AVX-512F) с инструкциями по обнаружению конфликтов Intel AVX-512 (AVX-512CD), Экспоненциальные и взаимные инструкции Intel AVX-512 (AVX-512ER) и инструкции предварительной выборки Intel AVX-512 (AVX-512PF). Поддержка IMCI была удалена в пользу AVX-512.

Национальный научный вычислительный центр энергетических исследований объявил, что во второй фазе его новейшей суперкомпьютерной системы Cori будет использоваться Knights Landing Xeon Phi

20 июня 2016 года Intel представила семейство продуктов Intel Xeon Phi x200 на основе архитектуры Knights Landing, подчеркнув его применимость не только к традиционным рабочим нагрузкам моделирования, но и к машинному обучению. Модельный ряд, объявленный при запуске, включал только Xeon Phi загрузочного форм-фактора, но две его версии: стандартные процессоры и процессоры со встроенной архитектурой Intel Omni-Path. Последний обозначается суффиксом F в номере модели. Ожидается, что интегрированная матрица обеспечит лучшую задержку при меньшей стоимости, чем дискретные высокопроизводительные сетевые карты.

14 ноября 2016 года 48-й список TOP500 содержал 10 систем, использующих платформы Knights Landing.

Вариант сопроцессора Knight's Landing на базе PCIe никогда не предлагался для широкого рынка и был снят с производства к августу 2017 года. Сюда входили сопроцессорные карты 7220A, 7240P и 7220P.

Intel объявила, что прекращает выпуск Knights Landing летом 2018 года.

Все модели могут увеличивать свои пиковые скорости, добавляя 200 МГц к их базовой частоте при работе всего лишь с одним или двумя ядрами. При работе от трех до максимального количества ядер микросхемы могут увеличивать частоту только на 100 МГц выше базовой. Все чипы выполняют код высокого разрешения AVX с частотой, уменьшенной на 200 МГц.

| Xeon Phi. 7200 Series | sSpec. Number | Cores. (Threads) | Тактовая частота (МГц) | L2. Кэш | Память MCDRAM | Память DDR4 | Пиковая DP. Расчетная | TDP. (Вт) | Socket | Дата выпуска | Номер детали | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Base | Turbo | Количество | BW | Емкость | BW | |||||||||

| Xeon Phi 7210 | SR2ME (B0) | 64 (256) | 1300 | 1500 | 32 МБ | 16 ГБ | 400+ ГБ / с | 384 ГБ | 102,4 ГБ / с | 2662. GFLOPS | 215 | SVLCLGA3647 | 20 июня 2016 г. | HJ8066702859300 |

| SR2X4 (B0) | ||||||||||||||

| Xeon Phi 7210F | SR2X5 (B0) | 230 | HJ8066702975000 | |||||||||||

| Xeon Phi 7230 | SR2MF (B0) | 215 | HJ8066702859400 | |||||||||||

| SR2X3 (B0) | ||||||||||||||

| Xeon Phi 7230F | SR2X2 (B0) | 230 | HJ8066702269002 | |||||||||||

| Xeon Phi 7250 | SR2MD (B0) | 68 (272) | 1400 | 1600 | 34 МБ | 3046. GFLOPS | 215 | HJ8066702859200 | ||||||

| SR2X1 (B0) | ||||||||||||||

| Xeon Phi 7250F | SR2X0 (B0) | 230 | HJ8066702268900 | |||||||||||

| Xeon Phi 7290 | SR2WY (B0) | 72 (288) | 1500 | 1700 | 36 МБ | 3456. GFLOPS | 245 | HJ8066702974700 | ||||||

| Xeon Phi 7290F | SR2WZ (B0) | 260 | HJ8066702975200 | |||||||||||

Knights Hill - это кодовое название архитектуры MIC третьего поколения, первые подробности которой Intel объявила на SC14. Он должен был производиться по 10-нм техпроцессу.

Knights Hill предполагалось использовать в Министерстве энергетики США суперкомпьютер Aurora, который будет развернут в Аргоннская национальная лаборатория. Однако Aurora была отложена в пользу использования «продвинутой архитектуры» с упором на машинное обучение.

В 2017 году Intel объявила, что Knights Hill был отменен в пользу другой архитектуры, построенной с нуля, чтобы позволить Exascale computing в будущем. Эта новая архитектура ожидается в 2020–2021 годах.

Knights Mill - это кодовое название Intel для продукта Xeon Phi, специализирующегося на глубоком обучении, первоначально выпущенного в декабре 2017. Практически идентичный по характеристикам Knights Landing, Knights Mill включает оптимизацию для лучшего использования инструкций AVX-512 и обеспечивает четырехстороннюю гиперпоточность. Повышена производительность с плавающей запятой одинарной и переменной точности за счет производительности с плавающей запятой двойной точности.

| Xeon Phi. 72x5 Series | Номер sSpec | Ядра. (Потоки) | Тактовая частота (МГц) | L2. Кэш | Память MCDRAM | Память DDR4 | Пиковая DP. Вычисления | TDP. (Вт) | Разъем | Дата выпуска | Номер детали | |||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| Базовая | Турбо | Количество | BW | Емкость | BW | |||||||||

| Xeon Phi 7235 | SR3VF (A0) | 64 (256) | 1300 | 1400 | 32 МБ | 16 ГБ | 400+ ГБ / с | 384 ГБ | 102,4 ГБ / с | TBA | 250 | SVLCLGA3647 | 4 квартал 2017 г. | HJ8068303823900 |

| Xeon Phi 7285 | SR3VE (A0) | 68 (272) | 1300 | 1400 | 34 МБ | 115,2 ГБ / с | TBA | 250 | HJ8068303823800 | |||||

| Xeon Phi 7295 | SR3VD (A0) | 72 (288) | 1500 | 1600 | 36 МБ | 115,2 ГБ / с | TBA | 320 | HJ8068303823700 | |||||

Исследователи провели эмпирическое исследование производительности и возможности программирования. авторы которой утверждают, что для достижения высокой производительности с помощью Xeon Phi по-прежнему требуется помощь программистов и что простое использование компиляторов с традиционными моделями программирования еще далеко от реальности. Однако исследования в различных областях, таких как науки о жизни и глубокое обучение, показали, что использование как потокового, так и SIMD-параллелизма Xeon Phi позволяет значительно ускорить работу.

| На Викискладе есть материалы, связанные с Intel MIC. |