С 1985 года многие процессоры, реализующие ту или иную версию архитектуры MIPS, были разработаны и широко используются.

Конвейерный MIPS, показывающий пять этапов: выборка инструкций, декодирование инструкций, выполнение, доступ к памяти и обратная запись.

Конвейерный MIPS, показывающий пять этапов: выборка инструкций, декодирование инструкций, выполнение, доступ к памяти и обратная запись. Первый микропроцессор MIPS, R2000, был анонсирован в 1985 году. Он добавил многоцикловые команды умножения и деления в несколько независимом блоке на кристалле. Были добавлены новые инструкции для извлечения результатов из этого устройства обратно в файл регистра процессора ; эти инструкции по получению результатов были взаимосвязаны.

R2000 можно было загрузить с прямым или обратным порядком байтов. У него был тридцать один 32-битный регистр общего назначения, но не было регистра состояния ( регистр кода состояния (CCR), разработчики считали его потенциальным узким местом), функции, которую он разделяет с AMD 29000, DEC Alpha и RISC-V.. В отличие от других регистров, счетчик программы не доступен напрямую.

R2000 также поддерживал до четырех сопроцессоров, один из которых был встроен в главный центральный процессор (ЦП) и обрабатывал исключения, ловушки и управление памятью, а остальные три были оставлены для других целей. Один из них мог быть заполнен дополнительным блоком с плавающей запятой (FPU) R2010, который имел тридцать два 32-битных регистра, которые можно было использовать как шестнадцать 64-битных регистров для двойной точности.

R3000 следовал за R2000 в 1988 году, добавив 32 KB (вскоре повышен до 64 КБ) кэширует для получения инструкций и данных, а также поддержки совместно используемой памяти многопроцессорной в виде когерентности кэша - протокол. Хотя в поддержке многопроцессорной обработки R3000 были недостатки, она успешно использовалась в нескольких успешных многопроцессорных компьютерах. R3000 также имел встроенный блок управления памятью (MMU), что было обычным явлением для процессоров того времени. R3000, как и R2000, может работать в паре с FPU R3010. R3000 был первым успешным разработчиком MIPS на рынке, и в итоге было выпущено более миллиона. Более быстрая версия R3000, работающая на частоте до 40 МГц, R3000A обеспечивает производительность 32 миллиона инструкций в секунду (MIPS) или VAX Unit of Performance (VUP). MIPS R3000A -Совместим R3051 работает на 33.8688 МГц был процессор, используемый в Sony PlayStation, хотя у него не было FPU или MMU. Сторонние проекты включают Performance Semiconductor в R3400 и IDT в R3500, оба они были R3000As с интегрированным R3010 FPU. Toshiba «s R3900 был практически первой системой на чипе (SoC) для ранних карманных компьютеров, которые бежали Windows CE. Радиационно-закаленного вариант для космического использования, Мангуст-V, является R3000 с интегрированным R3010 FPU.

Серия R4000, выпущенная в 1991 году, расширила MIPS до полного 64-битного дизайна слов, переместила FPU на основной кристалл, чтобы сформировать однокристальный микропроцессор, и имела тогда высокую тактовую частоту 100 МГц на момент введения. Однако для достижения тактовой частоты кеши были уменьшены до 8 КБ каждый, и для доступа к ним потребовалось три цикла. Высокие тактовые частоты были достигнуты с помощью метода глубокой конвейерной обработки (в то время называемого супер-конвейерной обработкой). В 1993 году последовал усовершенствованный R4400. Он имел больший размер первичного кэша 16 КБ, в основном безошибочную 64-битную работу и поддержку большего размера кэша L2.

MIPS, ныне подразделение Silicon Graphics (SGI) под названием MTI, разработало недорогой R4200, который стал основой для еще более дешевого R4300i. Производное от этого микропроцессора, NEC VR4300, использовалось в игровой консоли Nintendo 64.

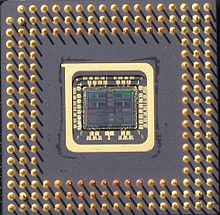

Вид снизу корпуса R4700 Orion с обнаженным кремниевым чипом, изготовленный IDT, разработанный Quantum Effect Devices

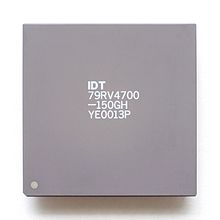

Вид снизу корпуса R4700 Orion с обнаженным кремниевым чипом, изготовленный IDT, разработанный Quantum Effect Devices  Упаковка для R4700 Orion, вид сверху

Упаковка для R4700 Orion, вид сверху Quantum Effect Devices (QED), отдельная компания, основанная бывшими сотрудниками MIPS, разработала R4600 Orion, R4700 Orion, R4650 и R5000. В то время как R4000 увеличил тактовую частоту и принес в жертву емкость кэша, в проектах QED упор делался на большие кеши, к которым можно было получить доступ всего за два цикла, и эффективное использование площади кремния. R4600 и R4700 использовались в недорогих версиях рабочей станции SGI Indy, а также в первых маршрутизаторах Cisco на базе MIPS, таких как маршрутизаторы серий 36x0 и 7x00. R4650 был использован в оригинальной WebTV приставках ( в настоящее время Microsoft TV). R5000 FPU имел более гибкое планирование с плавающей точкой одинарной точности, чем R4000, и, как следствие, R5000 на основе SGI Indys имела гораздо лучшую графическую производительность, чем аналогично с тактовой частотой R4400 Indys с тем же графическим оборудованием. SGI дала старой графической плате новое имя, когда она была объединена с R5000, чтобы подчеркнуть улучшение. Позже QED разработала семейство устройств RM7000 и RM9000 для рынков встраиваемых систем, таких как компьютерные сети и лазерные принтеры. QED была приобретена производителем полупроводников PMC-Sierra в августе 2000 года, последняя компания продолжала инвестировать в архитектуру MIPS. RM7000 включен интегрированный кэш 256 Кб L2 и контроллер для дополнительного кэша L3. RM9xx0 было семейством SOC устройств, которые включены северные мост периферийных устройств, такие как контроллер памяти, PCI контроллер, Gigabit Ethernet, контроллер и быстрый ввод / вывод, такие как HyperTransport порт.

R8000 (1994) был первым суперскалярная дизайн MIPS, способный выполнять две или целое число с плавающей точкой и две команды за один цикл памяти. Дизайн был распределен по шести микросхемам: целочисленный блок (с 16 КБ инструкций и 16 КБ кэшей данных), блок с плавающей запятой, три полностью настраиваемых ОЗУ тегов вторичного кэша (два для доступа к вторичному кэшу, один для отслеживания шины), и ASIC контроллера кеша. В конструкции было два полностью конвейерных блока умножения и сложения с двойной точностью, которые могли передавать данные из внекристального вторичного кэша объемом 4 МБ. R8000 работал на серверах SGI POWER Challenge в середине 1990-х годов, а позже стал доступен на рабочих станциях POWER Indigo2. Хотя его производительность FPU достаточно хорошо подходит научным пользователям, его ограниченная целочисленная производительность и высокая стоимость уменьшили привлекательность для большинства пользователей. R8000 был продан всего год и остается довольно редким.

В 1995 году был выпущен R10000. Этот процессор был однокристальным, работал на более высокой тактовой частоте, чем R8000, и имел более крупные кэши первичных инструкций и данных размером 32 КБ. Он также был суперскалярным, но его главным нововведением было исполнение вне очереди. Даже с одним конвейером памяти и более простым FPU, значительно улучшенная целочисленная производительность, более низкая цена и более высокая плотность сделали R10000 предпочтительным для большинства клиентов.

Некоторые более поздние разработки были основаны на ядре R10000. В R12000 использовался процесс 0,25 микрометра для сжатия кристалла и достижения более высоких тактовых частот. Пересмотренный R14000 позволил повысить тактовую частоту с добавленной поддержкой двойной скорости передачи данных синхронной динамической памяти с произвольным доступом ( DDR SDRAM ), статической оперативной памяти (SRAM) во внекристальной кэш - памяти. Более поздние версии называются R16000 и R16000A и отличаются более высокими тактовыми частотами и меньшим объемом изготовления кристаллов по сравнению с предыдущими версиями.

Другие члены семейства MIPS включают R6000, реализацию логики с эмиттерной связью (ECL), произведенную Bipolar Integrated Technology. R6000 представил архитектуру MIPS II. Его резервный буфер трансляции (TLB) и архитектура кеша отличаются от всех других членов семейства MIPS. R6000 не обеспечил обещанных преимуществ в производительности, и, хотя он нашел применение в машинах Control Data, он быстро исчез с основного рынка.

В 1981 году Джон Л. Хеннесси начал проект « Микропроцессор без взаимосвязанных конвейерных стадий» ( MIPS ) в Стэнфордском университете для исследования технологии компьютера с сокращенным набором команд (RISC). Результаты его исследования убедили его в будущем коммерческом потенциале технологии, и в 1984 году он взял творческий отпуск, чтобы основать MIPS Computer Systems. Компания разработала новую архитектуру, которая также была названа MIPS, и представила первую реализацию MIPS, R2000, в 1985 году. R2000 был улучшен, и дизайн был представлен как R3000 в 1988 году. Эти 32-разрядные процессоры легли в основу их компания на протяжении 1980-х годов использовалась в основном в серии рабочих станций Silicon Graphics (SGI), а затем в рабочих станциях и серверах DECstation корпорации Digital Equipment Corporation. Коммерческие разработки SGI отклонились от Стэнфордского MIPS, реализовав большинство блокировок аппаратно, предоставляя полные инструкции умножения и деления (среди прочего). Разработками частично руководил архитектор программного обеспечения Эрл Киллиан, который разработал 64-битное расширение набора инструкций MIPS III и руководил работой над микроархитектурой R4000.

В 1991 MIPS выпустила первый 64-битный микропроцессор, в R4000. Однако у MIPS возникли финансовые трудности при выводе его на рынок. Дизайн был настолько важен для SGI, в то время одного из немногих основных клиентов MIPS, что SGI купила компанию в 1992 году, чтобы гарантировать, что дизайн не будет утерян. Новое дочернее предприятие SGI было названо MIPS Technologies.

В начале 1990-х годов MIPS начала лицензировать свои разработки сторонним поставщикам. Это оказалось довольно успешным из-за простоты ядра, что позволило ему найти множество применений, в которых раньше использовались гораздо менее способные компьютеры со сложным набором команд (CISC) с аналогичным количеством вентилей и стоимостью; они тесно связаны: цена ЦП обычно зависит от количества вентилей и количества внешних контактов. Sun Microsystems пыталась добиться аналогичного успеха, лицензируя свое ядро SPARC, но не достигла такого успеха. К концу 1990-х годов MIPS была лидером в области встраиваемых процессоров. По данным MIPS Technologies Inc., наблюдался экспоненциальный рост: в 1997 году было поставлено 48 миллионов процессоров на базе MIPS и 49% от общей доли рынка процессоров RISC. MIPS была настолько успешной, что SGI отделила MIPS Technologies в 1998 году. Половина дохода MIPS пришлась на лицензирование их проектов, в то время как большая часть остального была получена от контрактных работ по проектированию ядер для третьих сторон.

В 1999 году компания MIPS Technologies заменила предыдущие версии архитектуры MIPS двумя архитектурами: 32-разрядной MIPS32 (на основе MIPS II с некоторыми добавленными функциями из MIPS III, MIPS IV и MIPS V) и 64-разрядной MIPS64 (на основе на MIPS V) для лицензирования. Nippon Electric Corporation ( NEC ), Toshiba и SiByte (позже приобретенная Broadcom ) получили лицензии на MIPS64, как только об этом было объявлено. С тех пор к ним присоединились Philips, LSI Logic и Integrated Device Technology (IDT). Сегодня ядра MIPS являются одними из наиболее часто используемых «тяжелых» ядер на рынке компьютерных устройств: карманных компьютеров, телевизионных приставок и т. Д.

Поскольку архитектура MIPS является лицензируемой, она привлекла несколько процессоров старт-ап компании на протяжении многих лет. Одним из первых разработчиков процессоров MIPS была компания Quantum Effect Devices (см. Следующий раздел). Команда разработчиков MIPS, разработавшая R4300i, основала компанию SandCraft, которая разработала R5432 для NEC, а затем выпустила SR71000, один из первых процессоров исполнения вне очереди для рынка встраиваемых систем. Первоначальная команда DEC StrongARM в конечном итоге разделилась на два стартапа на базе MIPS: SiByte, которая произвела SB-1250, одну из первых высокопроизводительных систем на кристалле (SOC) на основе MIPS ; в то время как Alchemy Semiconductor (позже приобретенная AMD ) производила SoC Au-1000 для использования с низким энергопотреблением. Lexra использовала архитектуру, подобную MIPS, и добавила расширения DSP для рынка аудиочипов и поддержку многопоточности для рынка сетей. Из-за того, что Lexra не лицензировала архитектуру, между двумя компаниями было возбуждено два судебных процесса. Первое было быстро решено, когда Lexra пообещала не рекламировать свои процессоры как MIPS-совместимые. Второй (о патенте MIPS 4814976 для обработки невыровненного доступа к памяти) был затяжным, нанес ущерб бизнесу обеих компаний и завершился тем, что MIPS Technologies предоставила Lexra бесплатную лицензию и крупную выплату наличными.

Появились две компании, специализирующиеся на создании многоядерных процессорных устройств с использованием архитектуры MIPS. Компания Raza Microelectronics, Inc. купила линейку продуктов у вышедшей из строя SandCraft, а затем выпустила устройства с восемью ядрами для телекоммуникационного и сетевого рынков. Cavium, первоначально производитель процессоров безопасности, также производил устройства с восемью ядрами ЦП, а затем и с 32 ядрами для тех же рынков. Обе эти фирмы разработали свои ядра собственными силами, только лицензируя архитектуру, а не покупая ядра у MIPS.

Среди производителей, которые создали системы компьютерных рабочих станций с использованием процессоров MIPS, - SGI, MIPS Computer Systems, Inc., Whitechapel Workstations, Olivetti, Siemens-Nixdorf, Acer, Digital Equipment Corporation, NEC и DeskStation.

Операционные системы портирована на архитектуру включают компании SGI IRIX, Microsoft 's Windows NT (через v4.0), Windows CE, Linux, FreeBSD, NetBSD, OpenBSD, UNIX System V, SINIX, QNX и MIPS Computer Systems' собственный RISC / ОС.

В начале 1990-х годов ходили слухи, что MIPS и другие мощные процессоры RISC обгонят архитектуру Intel IA-32. Этому способствовала поддержка двух первых версий Microsoft «s Windows NT для Альфы, MIPS и PowerPC, и в меньшей степени архитектуры Clipper и SPARC. Однако, поскольку Intel быстро выпустила более быстрые версии своих процессоров класса Pentium, Microsoft Windows NT v4.0 отказалась от поддержки чего-либо, кроме IA-32 и Alpha. С решением SGI о переходе на архитектуры Itanium и IA-32 в 2007 году (после банкротства по Главе 11 в 2006 году) и приобретением в 2009 году Rackable Systems, Inc., поддержка потребительского рынка MIPS / IRIX прекратилась в декабре 2013 года, как и первоначально. Запланированное. Тем не менее, группа поддержки все еще существует для особых случаев и отремонтированных систем, которые все еще доступны в ограниченном количестве.

Ingenic JZ4730 является примером для архитектуры MIPS на основе SoC.

Ingenic JZ4730 является примером для архитектуры MIPS на основе SoC. В течение 1990-х годов архитектура MIPS получила широкое распространение на рынке встраиваемых систем, в том числе для использования в компьютерных сетях, телекоммуникациях, аркадных играх, игровых консолях, компьютерных принтерах, цифровых приставках, цифровых телевизорах, DSL и кабельных модемах, а также персональные цифровые помощники.

Низкое энергопотребление и тепловые характеристики встроенных реализаций MIPS, широкая доступность встроенных средств разработки и знание архитектуры означают, что использование микропроцессоров MIPS во встроенных ролях, вероятно, останется обычным явлением.

В последние годы большая часть технологий, используемых в различных поколениях MIPS, предлагалась в качестве полупроводниковых ядер интеллектуальной собственности (IP-ядер), в качестве строительных блоков для конструкций встроенных процессоров. Обе 32-разрядные и 64-разрядные основные стержни предлагаются, известный как 4К и 5К. Эти ядра могут быть смешаны с дополнительными модулями, такими как модули с плавающей запятой (FPU), одиночные инструкции, системы с несколькими данными ( SIMD ), различные устройства ввода / вывода (I / O) и т. Д.

Ядра MIPS были коммерчески успешными, теперь они используются во многих бытовых и промышленных целях. Ядра MIPS можно найти в более новых маршрутизаторах Cisco, Linksys и Mikrotik, кабельных модемах и модемах с асимметричной цифровой абонентской линией (ADSL), смарт-картах, двигателях лазерных принтеров, телевизионных приставках, роботах и портативных компьютерах. В мобильных телефонах и КПК MIPS в значительной степени не смогла вытеснить существующую конкурирующую архитектуру ARM.

Процессоры архитектуры MIPS включают: IDT RC32438; ATI / AMD Xilleon ; Алхимия Au1000, 1100, 1200; Broadcom Sentry5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx и CN5xxx; Infineon Technologies EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2; Microchip Technology PIC32; NEC EMMA и EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR4300, VR5432, VR5500; Генерация Дубовых Технологий ; PMC-Sierra RM11200; QuickLogic QuickMIPS ESP; Toshiba Donau, Toshiba TMPR492x, TX4925, TX9956, TX7901; КОМДИВ-32, КОМДИВ-64, ЭЛЬВИС Мультикор из России.

Одно интересное, менее распространенное использование архитектуры MIPS - суперкомпьютеры с большим количеством процессоров. Silicon Graphics (SGI) переориентировала свой бизнес с настольных графических рабочих станций на рынок высокопроизводительных вычислений в начале 1990-х годов. Успех первой попытки компании создать серверные системы, серия Challenge, основанная на R4400 и R8000, а затем и на R10000, подтолкнула SGI к созданию гораздо более мощной системы. Внедрение интегрированного R10000 позволило SGI создать систему Origin 2000, в конечном итоге масштабируемую до 1024 ЦП с использованием межсоединения NUMAlink cc-NUMA. Origin 2000 породил серию Origin 3000, которая превысила максимальное количество ЦП в 1024, но использовала чипы R14000 и R16000 с тактовой частотой до 700 МГц. Ее суперкомпьютеры на базе MIPS были сняты с производства в 2005 году, когда SGI приняла стратегическое решение перейти на архитектуру Intel Itanium IA-64.

Стартап в области высокопроизводительных вычислений под названием SiCortex представил в 2007 году суперкомпьютер на основе массового параллелизма на базе MIPS. Машины основаны на архитектуре MIPS64 и высокопроизводительном межсоединении с использованием топологии графа Каутца. Система очень энергоэффективна и вычислительно мощна. Самый инновационный аспектом системы является ее обрабатывающим узлом многоядерной, который объединяет шесть MIPS64 ядер, A матричный переключатель контроллер памяти, соединить прямой доступ к памяти (DMA), двигатель, Gigabit Ethernet и PCI Express контроллеры все на одном чипе, который потребляет всего 10 ватт мощность, но имеет пиковую производительность с плавающей запятой 6 гига FLOPS. Самая мощная конфигурация, SC5832, представляет собой суперкомпьютер с одним шкафом, состоящий из 972 таких узловых микросхем, что в общей сложности составляет 5832 процессорных ядра MIPS64 и максимальная производительность 8,2 терафлопс.

Loongson - это семейство MIPS-совместимых микропроцессоров, разработанных Институтом вычислительных технологий (ICT) Китайской академии наук. Независимо разработанные китайцами, ранние модели не поддерживали четыре инструкции, запатентованные MIPS Technologies. В июне 2009 года ICT лицензировала архитектуры MIPS32 и MIPS64 от MIPS Technologies. Начиная с 2006 года, многие компании выпустили компьютеры на базе Loongson, в том числе неттопы и нетбуки, предназначенные для использования с низким энергопотреблением.

В последние годы специальный космический чип Loongson (1E04 / 1E0300 / 1E1000,1F04 / 1F0300,1J) использовался на 3-5 навигационных спутниках Beidou.

Суперкомпьютер Dawning 6000, который имеет прогнозируемую производительность более 1 P FLOPS, будет использовать процессор Loongson. Dawning 6000 в настоящее время разрабатывается совместно компаниями ICT и Dawning Information Industry. Ли Гоцзе, председатель компании Dawning Information Industry и директор и академик ICT, сказал, что исследования и разработки Dawning 6000, как ожидается, будут завершены через два года. К тому времени ожидается, что высокопроизводительные компьютеры китайского производства достигнут двух основных целей: во-первых, внедрение процессоров отечественного производства; во-вторых, существующая кластерная структура системы высокопроизводительных компьютеров будет изменена, когда производительность достигнет 1 PFLOPS.

Анонсированное в 2012 году семейство MIPS Aptiv включает три 32-разрядных процессора на базе архитектуры MIPS32 Release 3.

microAptiv - это компактное встроенное процессорное ядро реального времени с пятиступенчатым конвейером и набором команд сжатия кода microMIPS. microAptiv может быть сконфигурирован либо как микропроцессор (microAptiv UP) с кэшами инструкций и данных и блоком управления памятью, либо как микроконтроллер (microAptiv UC) с блоком защиты памяти (MPU). ЦП объединяет функции DSP и SIMD для удовлетворения требований к обработке сигналов для встраиваемых сегментов начального уровня, включая промышленное управление, интеллектуальные счетчики, автомобильную и проводную / беспроводную связь.

interAptiv - это многопроцессорное ядро, использующее девятиступенчатый конвейер с многопоточностью. Ядро может использоваться для высокопараллельных задач, требующих оптимизации затрат и энергопотребления, таких как интеллектуальные шлюзы, обработка основной полосы частот в пользовательском оборудовании LTE и малых сотах, контроллеры твердотельных накопителей (SSD) и автомобильное оборудование.

proAptiv - это суперскалярное ядро процессора, работающее вне очереди, которое доступно в одно- и многоядерных версиях продукта. proAptiv разработан для обработки приложений в подключенной бытовой электронике и обработки уровня управления в сетях.

Анонсированное в июне 2013 года семейство MIPS Warrior включает в себя несколько 32-разрядных и 64-разрядных процессоров, основанных на архитектурах MIPS Release 5 и 6.

32-битные ядра MIPS для встраиваемых систем и микроконтроллеров:

64-битные процессоры MIPS для высокопроизводительных встроенных систем с низким энергопотреблением:

32-битные и 64-битные процессоры приложений MIPS: