Микроконтроллер Intel P8051 Микроконтроллер Intel P8051 |

Intel MCS-51 (обычно называют 8051) представляет собой однокристальный микроконтроллер серии (MCU), разработанный Intel в 1980 году для использования в встраиваемых системах. Архитектором набора команд Intel MCS-51 был Джон Х. Уортон. Оригинальные версии Intel были популярны в 1980-х и начале 1990-х годов, а расширенные бинарно-совместимые производные остаются популярными и сегодня. Это пример компьютера со сложным набором команд (но он также обладает некоторыми особенностями архитектуры RISC, такими как большой набор регистров и окна регистров ) и имеет отдельные области памяти для программных инструкций и данных.

Первоначальное семейство Intel MCS-51 было разработано с использованием технологии металл-оксид-полупроводник ( NMOS ) N-типа, как и его предшественник Intel MCS-48, но более поздние версии, обозначенные буквой C в их названии (например, 80C51), используют дополнительный металл - оксидно-полупроводниковая ( CMOS ) технология и потребляют меньше энергии, чем их предшественники NMOS. Это сделало их более подходящими для устройств с батарейным питанием.

Семейство было продолжено в 1996 году с улучшенным 8-битным MCS-151 и семейством 8/ 16 / 32-битных MCS-251 двоично-совместимых микроконтроллеров. Хотя Intel больше не производит семейства MCS-51, MCS-151 и MCS-251, улучшенные бинарно-совместимые производные, выпускаемые многочисленными поставщиками, остаются популярными и сегодня. Некоторые производные интегрируют процессор цифровых сигналов (DSP). Помимо этих физических устройств, несколько компаний также предлагают производные MCS-51 в качестве IP-ядер для использования в конструкциях программируемых вентильных матриц (FPGA) или специализированных интегральных схем (ASIC).

i8051 микроархитектура

i8051 микроархитектура  i8051 распиновка

i8051 распиновка Архитектура 8051 предоставляет множество функций ( центральный процессор (ЦП), оперативная память (ОЗУ), постоянная память (ПЗУ), порты ввода / вывода (I / O), последовательный порт, управление прерываниями, таймеры ) в одном устройстве. пакет :

Одной из особенностей ядра 8051 является включение механизма логической обработки, который позволяет выполнять логические операции на уровне битов напрямую и эффективно над выбранными внутренними регистрами, портами и выбранными ячейками ОЗУ. Другой особенностью является включение четырех наборов рабочих регистров с возможностью выбора банка, что значительно сокращает время, необходимое для выполнения переключений контекста для входа и выхода из подпрограмм обслуживания прерывания. С помощью одной инструкции 8051 может переключать банки регистров, избегая трудоемкой задачи по переносу критических регистров в ОЗУ.

После того, как UART и таймер, если необходимо, были настроены, программисту нужно только написать простую процедуру прерывания, чтобы пополнять регистр сдвига отправки всякий раз, когда UART сдвигает последний бит и / или очищает регистр сдвига полного приема (копия данные в другом месте). Затем основная программа выполняет последовательное чтение и запись, просто считывая и записывая 8-битные данные в стеки.

По состоянию на 2013 год многие крупные производители микросхем все еще разрабатывают новые производные, а крупные поставщики компиляторов, такие как IAR Systems, Keil и Altium Tasking, постоянно выпускают обновления.

Микроконтроллеры на базе MCS-51 обычно включают в себя один или два UART, два или три таймера, 128 или 256 байтов внутренней ОЗУ данных (16 байтов из которых имеют побитовую адресацию), до 128 байтов ввода / вывода, от 512 байтов до 64 КБ внутренней программной памяти, а иногда и некоторого количества расширенной оперативной памяти данных (ERAM), расположенной во внешнем пространстве данных. Внешняя RAM и ROM совместно используют шины данных и адреса. Исходное ядро 8051 работало с 12 тактовыми циклами на машинный цикл, при этом большинство инструкций выполнялось за один или два машинных цикла. Таким образом, с тактовой частотой 12 МГц 8051 может выполнять 1 миллион одноцикловых инструкций в секунду или 500000 двухтактных инструкций в секунду. В настоящее время широко используются усовершенствованные ядра 8051, которые работают с шестью, четырьмя, двумя или даже одной тактовой частотой за машинный цикл (обозначается «1T») и имеют тактовые частоты до 100 МГц, и, таким образом, способны к еще большему количеству инструкций в секунду. Все Silicon Labs, некоторые устройства Dallas (теперь часть Maxim Integrated ) и несколько устройств Atmel (теперь часть Microchip ) имеют одноцикловые ядра.

Варианты 8051 могут включать в себя встроенные таймеры сброса с обнаружением обесточивания, встроенные генераторы, самопрограммируемую память программ флэш-ПЗУ, встроенное внешнее ОЗУ, дополнительное внутреннее хранилище программ, код загрузчика в ПЗУ, энергонезависимое хранилище данных ЭСППЗУ., I 2 C, SPI и хост-интерфейсы USB, шина CAN или LIN, радиомодули ZigBee или Bluetooth, генераторы ШИМ, аналоговые компараторы, аналого-цифровые и цифро-аналоговые преобразователи, часы реального времени, дополнительные счетчики и таймеры, в - средства отладки схем, больше источников прерываний, дополнительные режимы энергосбережения, больше / меньше параллельных портов и т. д. Intel изготовила версию с программированием маски, 8052AH-BASIC, с интерпретатором BASIC в ПЗУ, способную запускать пользовательские программы, загруженные в ОЗУ.

Микроконтроллеры на базе MCS-51 адаптированы к экстремальным условиям. Примерами высокотемпературных вариантов являются семейство Tekmos TK8H51 от −40 ° C до +250 ° C или Honeywell HT83C51 от −55 ° C до +225 ° C (с работой до 1 года при +300 ° C). Доступны радиационно-стойкие микроконтроллеры MCS-51 для использования в космических аппаратах; например, от Cobham (ранее Aeroflex ) как UT69RH051 или от НИИЭТ как 1830VE32 ( русский : 1830ВЕ32).

В некоторых инженерных школах микроконтроллер 8051 используется во вводных курсах по микроконтроллерам.

8051 - это оригинальное название Intel с 4 КБ ПЗУ и 128 байт ОЗУ. Варианты, начинающиеся с 87, имеют программируемое пользователем ППЗУ, иногда стираемое УФ-излучением. Варианты с C в качестве третьего символа - это своего рода CMOS. 8031 и 8032 - это версии без ПЗУ, с ОЗУ 128 и 256 байт. Последняя цифра может указывать размер памяти, например, 8052 с 8 КБ ROM, 87C54 16 КБ EPROM и 87C58 с 32 КБ EPROM, все с 256 байтами RAM.

MCS-51 имеет четыре различных типа памяти: внутреннее ОЗУ, регистры специальных функций, память программ и внешняя память данных. Для эффективного доступа к ним некоторые компиляторы используют целых 7 типов определений памяти: внутреннее ОЗУ, однобитный доступ к внутренней ОЗУ, регистры специальных функций, однобитовый доступ к выбранным (делимым на 8) регистрам специальных функций, ОЗУ программ, доступ к внешнему ОЗУ осуществляется с использованием косвенного доступа к регистру с использованием одного из стандартных 8-разрядных регистров, а регистр косвенного доступа к внешнему ОЗУ с использованием 16-разрядного регистра косвенного доступа.

Набор команд 8051 спроектирован как гарвардская архитектура с раздельной памятью (данные и инструкции); он может выполнять только код, извлеченный из памяти программ, и не имеет инструкций для записи в память программ. Однако шина, выходящая из ИС, имеет один адрес и путь данных и сильно напоминает шину архитектуры фон Неймана.

Большинство систем 8051 соблюдают набор инструкций и требуют настраиваемых функций для загрузки новых исполняемых программ, например, во флэш-память.

Внутреннее ОЗУ (IRAM) имеет 8-битное адресное пространство с адресами от 0 до 0xFF. IRAM от 0x00 до 0x7F содержит 128 напрямую адресуемых 1-байтовых регистров, к которым можно получить доступ с помощью 8-битного абсолютного адреса, который является частью инструкции. В качестве альтернативы, доступ к IRAM можно получить косвенно: адрес загружается в R0 или R1, а доступ к памяти осуществляется с использованием синтаксиса @ R0 или @ R1 или как память стека через указатель стека SP с помощью операций PUSH и POP; и * операции CALL и RET.

Исходный 8051 имеет только 128 байт IRAM. 8052 добавил IRAM от 0x80 до 0xFF, к которому можно получить доступ только косвенно (например, для использования в качестве пространства стека). Большинство клонов 8051 также имеют полные 256 байтов IRAM.

Вместо этого прямой доступ к адресам 80-FF IRAM отображается в регистры специальных функций (SFR), где расположены аккумуляторы A, B, бит переноса C и другие специальные регистры для управления, состояния и т. Д.

Регистры специальных функций (SFR) расположены в том же адресном пространстве, что и IRAM, по адресам от 0x80 до 0xFF, и доступ к ним осуществляется напрямую с использованием тех же инструкций, что и для нижней половины IRAM. К ним нельзя получить доступ косвенно через @ R0 или @ R1 или указатель стека SP; косвенный доступ к этим адресам вместо этого будет иметь доступ ко второй половине IRAM.

Регистры специальных функций (SFR) включают аккумуляторы A (или ACC, в E0) и B (в F0) и слово состояния программы (или PSW, в D0) сами по себе, а также 16-битный указатель данных DPTR (в 82 как DPL и 83 как DPH). В дополнение к ним, небольшое ядро других регистров специальных функций - включая IE разрешения прерывания на A8 и IP приоритета прерывания на B8; порты ввода / вывода P0 (80), P1 (90), P2 (A0), P3 (B0); управление последовательным вводом / выводом SCON (98) и буфер SBUF (99); регистр управления CPU / питанием PCON (87); и регистры для таймеров 0 и 1 управления (TCON на 88) и режима работы (TMOD на 89), 16-битного таймера 0 (TL0 на 8A, TH0 на 8C) и таймера 1 (TL1 на 8B, TH1 на 8D) - присутствуют во всех версиях 8051. Остальные адреса зависят от версии; в частности, регистры таймера 2 для 8052: регистр управления T2CON (на C8), 16-битный захват / защелка (RCAP2L на CA, RCAP2H на CB) и таймер 2 (TL2 на CC и TH2 на CD), являются не входит в комплект 8051.

32 байта в IRAM из 0x00–0x1F содержат пространство для четырех восьмибайтовых окон регистров, которым сопоставляются 8 регистров R0 – R7. Текущее активное окно определяется двухбитным адресом, содержащимся в слове состояния программы.

16 байтов (128 бит) в ячейках IRAM 0x20–0x2F содержат пространство для 128 1-битных регистров, которые адресуются отдельно как битовые регистры 00-7F.

Остальные битовые регистры, адресованные как 80-FF, отображаются в 16 регистров специальных функций 80, 88, 90, 98,..., F0 и F8 (те, адреса которых кратны 8), и, следовательно, включают биты, содержащие аккумуляторы A, B и слово состояния программы PSW. Адрес окна регистров, являющийся битами 3 и 4 на PSW, сам адресуется как битовые регистры D3 и D4 соответственно; в то время как бит переноса C (или CY) в бите 7 PSW адресуется как битовый регистр D7.

Программная память (PMEM, хотя и менее распространенная, чем IRAM и XRAM) составляет до 64 КБ постоянной памяти, начиная с адреса 0 в отдельном адресном пространстве. Он может быть встроенным или внешним, в зависимости от конкретной модели используемого чипа. Программная память предназначена только для чтения, хотя некоторые варианты 8051 используют встроенную флэш-память и предоставляют метод перепрограммирования памяти в системе или в приложении.

Помимо кода, можно хранить данные только для чтения, такие как таблицы поиска, в программной памяти, полученные с помощью инструкций или. Адрес вычисляется как сумма 8-битного аккумулятора и 16-битного регистра (PC или DPTR). MOVC A,@A+DPTRMOVC A,@A+PC

Специальные инструкции перехода и вызова ( AJMPи ACALL) немного уменьшают размер кода, который обращается к локальной (в пределах тех же 2 КБ) программной памяти.

Когда требуется код размером более 64 КБ, обычная система переключает банк кодов с универсальным вводом-выводом, выбирающим старшие биты адреса. Некоторые компиляторы 8051 предусматривают автоматический доступ к постраничному коду. В этих системах векторы прерываний и таблица подкачки помещаются в первые 32 КБ кода и всегда являются резидентными.

Внешняя память данных (XRAM) - это третье адресное пространство, также начинающееся с адреса 0 и обеспечивающее 16-битное адресное пространство. Он также может быть встроенным или внекристальным; что делает его «внешним», так это то, что к нему нужно обращаться с помощью MOVXинструкции (move external). Многие варианты 8051 включают стандартные 256 байтов IRAM плюс несколько килобайт XRAM на кристалле.

Первые 256 байт XRAM могут быть доступны с помощью,, и инструкции. Доступ ко всем 64 КБ можно получить с помощью и. 16-битный адрес требует, чтобы программист загрузил 16-битный индексный регистр. По этой причине доступ к ОЗУ с 16-битными адресами значительно медленнее. MOVX A,@R0MOVX A,@R1MOVX @R0,AMOVX @R1,AMOVX A,@DPTRMOVX @DPTR,A

Некоторые процессоры позволяют 8-битному косвенному адресу использовать любой 8-битный регистр общего назначения.

Чтобы разрешить использование этой функции, некоторые 8051-совместимые микроконтроллеры с внутренней RAM размером более 256 байт или невозможностью доступа к внешней RAM обращаются к внутренней RAM, как если бы она была внешней, и имеют специальный функциональный регистр (например, PDATA), который позволяет им для установки верхнего адреса 256-байтовой страницы. Это имитирует режим MCS8051, который может вызывать старший байт адреса ОЗУ, устанавливая контакты ввода-вывода общего назначения.

Когда требуется ОЗУ больше 64 КБ, обычная система переключает банк ОЗУ с универсальным вводом-выводом, выбирающим старшие биты адреса. Некоторые компиляторы 8051 предусматривают автоматический доступ к выгружаемым данным.

Единственный регистр 8051, который не отображается в память, - это 16-битный счетчик программ (ПК). Это указывает адрес следующей инструкции для выполнения. Инструкции относительного ветвления предоставляют 8-битное смещение со знаком, которое добавляется к ПК.

Доступ к восьми регистрам общего назначения R0 – R7 можно получить с помощью инструкций на один байт короче других. Они отображаются в IRAM между 0x00 и 0x1F. В любой момент времени используются только восемь байтов из этого диапазона, что определяется двумя битами выбора банка в PSW.

Ниже приведен частичный список регистров 8051, которые отображены в памяти в пространство регистров специальной функции:

256 одиночных битов имеют прямую адресацию. Это 16 ячеек IRAM из 0x20–0x2F и 16 регистров специальных функций 0x80, 0x88, 0x90,..., 0xF8. К любому биту этих байтов можно получить прямой доступ с помощью множества логических операций и условных переходов.

Обратите внимание, что PSW не содержит общих отрицательных (N) или нулевых (Z) флагов. Для первого наиболее значимый бит аккумулятора может быть адресован напрямую, поскольку это SFR с побитовой адресацией. Для последнего есть явные инструкции для перехода к тому, равен ли аккумулятор нулю. Также существует операция сравнения и перехода по двум операндам.

Бит четности (P) часто используется для реализации последовательных режимов, которые включают проверку на четность. Для поддержки этого стандартные UART MCS51 могли передавать 9 бит.

Микроархитектура Intel MCS8051 является проприетарной, но опубликованные характеристики позволяют предположить, как она работает. Это многоцикловый процессор. MCS8051 использовал 12 тактов для большинства инструкций. Количество циклов на инструкцию (больше 8) предполагает, что у нее есть однобитовый арифметико-логический блок, который обрабатывает свои 8-битные данные по одному биту за раз. Это также может объяснить, почему он может экономично предоставлять однобитовые инструкции. Относительно большое количество циклов также, кажется, указывает на то, что он использует только один фронт своих часов. (Многие многоцикловые компьютеры используют свою логику с обеих сторон.)

Во многих инструкциях используется аккумулятор. Поскольку он имеет аккумулятор, ему может потребоваться, чтобы аккумулятор обеспечивал один вход из двух входов, необходимых его арифметико-логическому блоку. Это означает, что он имеет одну внутреннюю шину (экономичный дизайн), а не несколько шин от двухпортового массива регистров, которые могут питать обе стороны ALU. Чтобы снизить затраты, вместо использования мультиплексоров, он может включать и отключать устройства по своей шине, используя логические устройства с тремя состояниями. Последовательная шина с тремя состояниями также позволила бы создать экономичный однобитовый мультиплексор для его системы регистров с переключением банков.

Напротив, большинство совместимых компьютеров выполняют инструкции за один-три цикла, за исключением инструкций умножения и деления. Гораздо более высокая скорость - основная причина, по которой они заменили MCS8051 в большинстве приложений. Скорость предполагает, что они имеют восьмиразрядные внутренние шины и арифметико-логические блоки.

Каждое прерывание имеет четыре приоритета. В пределах каждого приоритета прерывания устройств имеют фиксированный приоритет. Таким образом, кажется, что контроллер прерываний определяет приоритеты прерываний с помощью четырех последовательных цепочек логических элементов, при этом каждое прерывание имеет логический элемент в каждой цепочке приоритета.

Все инструкции имеют длину от 1 до 3 байтов и состоят из начального байта кода операции, за которым следуют до 2 байтов операндов.

1 / 4 из байт коды операции, х 0- х 3, используются для нерегулярных опкодов.

3 / 4 из опкода байт, х 4- х F, назначены 16 основных инструкций ALU с 12 возможными операндами. Наименьший значащий полубайт кода операции выбирает основной операнд следующим образом:

INC operandDEC operandMOV operand,#dataCJNE operand,#data,offsetСамый старший полубайт определяет операцию следующим образом. Не все поддерживают все режимы адресации; непосредственный режим, в частности, недоступен, когда записывается основной операнд. Мнемоника инструкций использует место назначения, порядок исходных операндов.

INC operandINC ADEC operandDEC AADD A,operandRL A ADD A,AADDC A,operandRLC AADDC A,AORL A,operandORL address,#dataORL address,AANL A,operandANL address,#dataANL address,AXRL A,operandXRL address,#dataXRL address,AMOV operand,#dataMOV A,#dataMOV address,operandSUBB A,operandMOV operand,addressCJNE operand,#data,offset#dataи перейдите к PC + смещение, если оно не равно. Непосредственные и прямые режимы памяти (опкоды 0xB4 и 0xB5) сравнить операнд от аккумулятора,. Обратите внимание, что нет инструкции сравнения и перехода при равенстве.CJNE A,operand,offsetCJEXCH A,operandDJNZ operand,offsetMOV A,operandMOV operand,AТолько ADD, ADDCи SUBBинструкции, установленные PSW флаги. В INC, DECи логические инструкции нет. В CJNEмодифицирует инструкции С бит только в заема, что результаты операнд1 - operand2.

Нерегулярные инструкции содержат 64 кода операции, имеющих более ограниченные режимы адресации, плюс несколько кодов операции, извлеченных из неприменимых режимов в обычных инструкциях.

| Код операции | х 0 | х 1 | х 2 | х 3 | х 4 |

|---|---|---|---|---|---|

| 0 у | NOP | LJMP addr16 | RR A (повернуть вправо) | INC A | |

| 1 год | JBC bit,offset (переход, если бит установлен с очищенным) | LCALL addr16 | RRC A (повернуть вправо через перенос) | DEC A | |

| 2 лет | JB bit,offset (переход, если установлен бит) | RET | RL A (повернуть налево) | ADD A,#data | |

| 3 лет | JNB bit,offset (прыгать, если бит очищен) | RETI | RLC A (повернуть влево через перенос) | ADDC A,#data | |

| 4 лет | JC offset (прыгать, если набор для переноски) | ORL address,A | ORL address,#data | ORL A,#data | |

| 5 лет | JNC offset (прыгать, если несёт ясно) | ANL address,A | ANL address,#data | ANL A,#data | |

| 6 лет | JZ offset (прыгать, если ноль) | XRL address,A | XRL address,#data | XRL A,#data | |

| 7 лет | JNZ offset (прыгать, если не ноль) | ORL C,bit | JMP @A+DPTR | MOV A,#data | |

| 8 лет | SJMP offset (короткий прыжок) | ANL C,bit | MOVC A,@A+PC | DIV AB | |

| 9 лет | MOV DPTR,#data16 | MOV bit,C | MOVC A,@A+DPTR | SUBB A,#data | |

| А у | ORL C,/bit | MOV C,bit | INC DPTR | MUL AB | |

| B y | ANL C,/bit | CPL bit | CPL C | CJNE A,#data,offset | |

| C y | PUSH address | CLR bit | CLR C | SWAP A | |

| D y | POP address | SETB bit | SETB C | DA A (десятичная корректировка) | |

| E y | MOVX A,@DPTR | MOVX A,@R0 | MOVX A,@R1 | CLR A | |

| F y | MOVX @DPTR,A | MOVX @R0,A | MOVX @R1,A | CPL A |

CJNE A,address,offsetXCHD A,@R0–1 обменять младший полубайт операндов.Код SJMPоперации (короткий переход) принимает байт-операнд относительного смещения со знаком и передает туда управление относительно адреса следующей инструкции. В AJMP/ ACALLопкодах объединить три наиболее значимых биты байта кода операции со следующим байтом, чтобы указать 11-битное назначение, который используется для замены 11 нижних бит регистра PC (верхние 5 бит регистра PC остаются нетронутыми). Для больших адресов, то LJMPи LCALLинструкции позволяют 16-битное назначение.

Одна из причин популярности 8051 - диапазон операций с отдельными битами. Биты всегда указываются по абсолютным адресам; не существует косвенной регистровой или индексированной адресации. Инструкции, которые работают с отдельными битами:

SETB bit,,: Установить, очистить или дополнить указанный битCLR bitCPL bitJB bit,offset: Перейти, если установлен битJNB bit,offset: Перейти, если бит сброшенJBC bit,offset: Переход, если бит установлен, и сброс битаMOV C,bit,: Переместить указанный бит в бит переноса или наоборот.MOV bit,CORL C,bit,: Или бит (или его дополнение) к биту переносаORL C,/bitANL C,bit,: И бит (или его дополнение) к биту переносаANL C,/bitВ форме записывается битовый операнд address.number. Поскольку флаг переноса представляет собой бит 7 слова состояния программы с побитовой адресацией, команды, и являются более короткими эквивалентами, и. SETB CCLR CCPL CSETB PSW.7CLR PSW.7CPL PSW.7

Хотя для большинства инструкций требуется, чтобы один операнд был аккумулятором или непосредственной константой, код операции 0x85 работает MOVнепосредственно между двумя внутренними ячейками ОЗУ.

Существуют различные компиляторы языков программирования высокого уровня для 8051. Для 8051 доступно несколько компиляторов C, большинство из которых позволяет программисту указать, где каждая переменная должна храниться в шести типах памяти, и предоставить доступ к конкретному оборудованию 8051. такие функции, как несколько банков регистров и инструкции по манипулированию битами. Есть много коммерческих компиляторов C. Компилятор C для малых устройств (SDCC) - популярный компилятор C. Другие языки высокого уровня, такие как C ++, Forth, BASIC, Object Pascal, Pascal, PL / M и Modula-2, доступны для 8051, но они менее широко используются, чем C и ассемблер.

Поскольку IRAM, XRAM и PMEM (только для чтения) имеют адрес 0, компиляторы C для архитектуры 8051 предоставляют специфичные для компилятора прагмы или другие расширения, чтобы указать, где должен храниться конкретный фрагмент данных (т. Е. Константы в PMEM или переменные, требующие быстрый доступ в IRAM). Поскольку данные могут находиться в одном из трех пространств памяти, обычно предоставляется механизм, позволяющий определить, к какой памяти относится указатель, либо путем ограничения типа указателя на включение пространства памяти, либо путем сохранения метаданных с указателем.

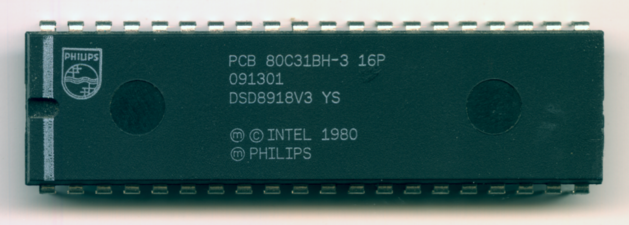

Микроконтроллеры Intel 8031

Микроконтроллеры Intel 8031  Микроконтроллер Intel D87C51

Микроконтроллер Intel D87C51 Intel прекратила выпуск своей линейки продуктов MCS-51 в марте 2007 года; тем не менее, существует множество усовершенствованных продуктов 8051 или интеллектуальной собственности на микросхемы, которые регулярно добавляются другими поставщиками.

Предшественник 8051, 8048, использовался в клавиатуре первого IBM PC, где он преобразовывал нажатия клавиш в последовательный поток данных, который отправляется на основной блок компьютера. Intel 8049 выполнял аналогичную роль в Sinclair QL. 8048 и его производные до сих пор используются для базовых моделей клавиатур.

8031 был уменьшенной версией оригинального 8051, которая не имела никакой внутренней памяти программы ( память только для чтения, ПЗУ). Чтобы использовать этот чип, необходимо было добавить внешнее ПЗУ, содержащее программу, которую 8031 будет извлекать и выполнять. Микросхема 8051 может быть продана как 8031 без ПЗУ, поскольку внутреннее ПЗУ 8051 отключено нормальным состоянием вывода EA в конструкции на основе 8031. Продавец может продать 8051 как 8031 по любому количеству причин, таких как неправильный код в ПЗУ 8051 или просто переизбыток 8051 и недостаток 8031.

8052 была расширенная версия оригинального 8051, который показал 256 байт внутренней памяти вместо 128 байт, 8 Кбайт ПЗУ вместо 4 КБ, а третий 16-битный таймер. Большинство современных 8051-совместимых микроконтроллеров включают эти функции.

8032 были такие же функции, что и 8052, кроме недоставало памяти программ внутреннего ПЗУ.

8751 был 8051 с 4 КБ EPROM вместо 4 КБ ПЗУ. Они были идентичны, за исключением энергонезависимой памяти. Эта деталь была доступна в керамическом корпусе с прозрачным кварцевым окном над кристаллом, чтобы УФ-свет можно было использовать для стирания EPROM. Связанные части: 8752 имел 8 КБ EPROM, 8754 имел 16 КБ EPROM, 8758 имел 32 КБ EPROM.

80C537 (ROM-менее) и 80C517 (8 KB ROM) является КМОП - версия, предназначенная для автомобильной промышленности. Улучшения в основном включают новые и улучшенные периферийные устройства. 80C5x7 имеет отказоустойчивые механизмы, средства обработки аналоговых сигналов, расширенные возможности таймера и 32-разрядное арифметическое периферийное устройство. Другие функции включают в себя:

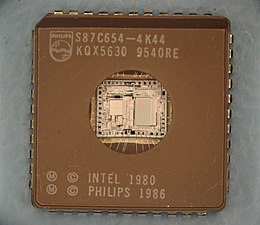

AMD D87C51

MHS S-80C31

OKI M80C31

Philips PCB80C31

Signetics SCN8031

Temic TS80C32

Более 20 независимых производителей производят процессоры, совместимые с MCS-51.

Infineon SAB-C515

Philips S87C654

Siemens SAB-C501

STC Micro STC89C52

Другие ИС или IP, совместимые с MCS-51, были разработаны компаниями Analog Devices, Integral Minsk, Кристалл Киев и НИИЭТ Воронеж.

Сегодня 8051 по-прежнему доступны в виде дискретных компонентов, но в основном они используются в качестве кремниевых ядер интеллектуальной собственности. Доступные в виде исходного кода на языке описания оборудования (например, VHDL или Verilog ) или в виде списков соединений FPGA, эти ядра обычно интегрируются во встроенные системы, в изделиях от USB-флэш-накопителей до стиральных машин и сложных систем беспроводной связи на кристалле. Разработчики используют кремниевые IP-ядра 8051 из-за меньшего размера и меньшей мощности по сравнению с 32-битными процессорами, такими как серия ARM Cortex-M, MIPS и BA22.

Современные ядра 8051 быстрее, чем предыдущие упакованные версии. Усовершенствования конструкции повысили производительность 8051 при сохранении совместимости с исходным набором инструкций MCS 51. Исходный Intel 8051 работал с 12 тактовыми циклами на машинный цикл, и большинство инструкций выполнялись за один или два машинных цикла. Типичная максимальная тактовая частота 12 МГц означала, что эти старые 8051 могли выполнять один миллион однократных инструкций или 500000 двухтактных инструкций в секунду. Напротив, усовершенствованные кремниевые IP-ядра 8051 теперь работают с одним тактовым циклом за машинный цикл и имеют тактовую частоту до 450 МГц. Это означает, что процессор, совместимый с 8051, теперь может выполнять 450 миллионов инструкций в секунду.

Существует несколько вариантов с дополнительным 16-битным процессором цифровых сигналов (DSP) (например, для кодирования / декодирования MP3 или Vorbis ) со скоростью до 675 миллионов инструкций в секунду (MIPS) и встроенным интерфейсом USB 2.0 или в качестве интеллектуальной собственности.

В 1996 году Intel анонсировала семейство MCS-151, вариант, работающий до 6 раз быстрее, полностью двоичный и совместимый с 8051 набором инструкций. В отличие от 8051 MCS-151 является конвейерным процессором с 16-битной внутренней кодовой шиной и в 6 раз больше. скорость. Семейство MCS-151 также было прекращено Intel, но широко доступно в бинарно-совместимых и частично улучшенных вариантах.

8/16/32-разрядный микроконтроллер 80251 с адресным пространством 16 МБ ( 24 бита ) и в 6 раз более быстрым циклом команд был представлен Intel в 1996 году. Он может работать как 8-битный 8051, имеет 24-битную линейную адресацию., 8-битный ALU, 8-битные инструкции, 16-битные инструкции, ограниченный набор 32-битных инструкций, 16 8-битных регистров, 16 16-битных регистров (8 16-битных регистров, которые не разделяют пространство с какими-либо 8-битных регистров и 8 16-битных регистров, которые содержат 2 8-битных регистра на 16-битный регистр) и 10 32-битных регистров (2 выделенных 32-битных регистра и 8 32-битных регистров, которые содержат 2 16-битных регистра). битовые регистры на 32-битный регистр).

Он содержит расширенные инструкции - см. Также руководство программиста - и более поздние варианты с более высокой производительностью, также доступные как интеллектуальная собственность (IP). Это 3-х ступенчатый конвейерный. Семейство MCS-251 также было прекращено Intel, но оно широко доступно в бинарно-совместимых и частично улучшенных вариантах от многих производителей.

![]() СМИ, связанные с MCS-51 на Викискладе?

СМИ, связанные с MCS-51 на Викискладе?