| Общая информация | |

|---|---|

| Запущен | 1993 г. |

| Снято с производства | 1996 г. |

| Разработано | Росс Технологии |

| Производительность | |

| Максимум. Тактовая частота процессора | От 40 МГц до 200 МГц |

| Архитектура и классификация | |

| Набор инструкций | SPARC V8 |

| Физические характеристики | |

| Ядра | |

HyperSPARC, под кодовым названием «Pinnacle», является микропроцессор, который реализует SPARC Version 8 набор инструкций архитектуры (ISA), разработанный Ross Technology для Cypress Semiconductor.

HyperSPARC был представлен в 1993 году и конкурировал с Sun Microsystems SuperSPARC. Раджу Вегесна был микроархитектором. HyperSPARC был основным конкурентом Sun Microsystem в середине 1990-х годов. Когда Fujitsu приобрела Росса у Cypress, новый владелец считал HyperSPARC более важным, чем SPARC64, разработанный HAL Computer Systems, также дочерней компанией Fujitsu, и это мнение разделяли аналитики.

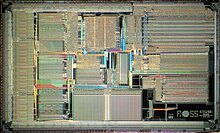

Фотография кристалла процессора Ross HyperSPARC II

Фотография кристалла процессора Ross HyperSPARC II HyperSPARC был двухпроцессорным суперскалярным микропроцессором. У него было четыре исполнительных блока: целочисленный блок, блок с плавающей запятой, блок загрузки / сохранения и блок ветвления. HyperSPARC имеет встроенный кэш команд объемом 8 КБ, из которого за цикл выбирались и декодировались две инструкции. Декодер не мог декодировать новые инструкции, если ранее декодированные инструкции не были переданы исполнительным блокам.

Файл целочисленных регистров содержал 136 регистров, обеспечивая восемь окон регистров, функция, определенная в SPARC ISA. У него было два порта чтения. Целочисленный блок имел четырехступенчатый конвейер, из которого были добавлены два этапа, так что конвейер будет равен всем конвейерам без плавающей запятой. Инструкции целочисленного умножения и деления, добавленные в версию V8 архитектуры SPARC, имели задержку 18 и 37 циклов соответственно и останавливали конвейер, пока они не были выполнены.

Микропроцессор поддерживает многопроцессорность в системах MBus.

HyperSPARC состоит из 1,2 миллиона транзисторов. Он был изготовлен компанией Cypress с использованием двухслойного металлического комплементарного процесса металл – оксид – полупроводник (КМОП) толщиной 0,65 мкм. Более поздние версии hyperSPARC имеют больше транзисторов из-за новых функций и были перенесены на новые процессы. Они были изготовлены Fujitsu, за исключением последней версии, которую изготовила NEC.

HyperSPARC был многочиповой конструкцией. Он был упакован в керамический многокристальный модуль (MCM) с решеткой на выводах (PGA).

В hyperSPARC использовался набор микросхем Cypress SparcSet, представленный в конце июля 1992 года. Он был разработан стартапом Nimbus Technologies, Inc. в Санта-Кларе, штат Калифорния, для Cypress, который и разработал дизайн. SparcSet также был совместим с другими микропроцессорами SPARC.