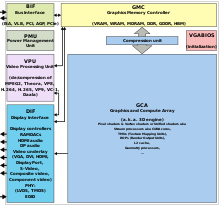

Общая блок-схема графического процессора. «Графическое ядро Next» относится ко всему графическому процессору; следовательно, возможно, что одна и та же версия GCA (3D-движок) сочетается с разными версиями DIF. AMD называет DIF (интерфейс дисплея) DCE (механизм контроллера дисплея). Например, графические процессоры Polaris имеют тот же GCA / GFX, что и их предшественники. Строго говоря, изначально GCN относилось исключительно к GCA.

Общая блок-схема графического процессора. «Графическое ядро Next» относится ко всему графическому процессору; следовательно, возможно, что одна и та же версия GCA (3D-движок) сочетается с разными версиями DIF. AMD называет DIF (интерфейс дисплея) DCE (механизм контроллера дисплея). Например, графические процессоры Polaris имеют тот же GCA / GFX, что и их предшественники. Строго говоря, изначально GCN относилось исключительно к GCA. Graphics Core Next (GCN ) - это кодовое имя для обеих серий микроархитектур а также для архитектуры набора команд . GCN был разработан AMD для их графических процессоров в качестве преемника микроархитектуры / набора команд TeraScale. Первый продукт с GCN был запущен 9 января 2012 года.

GCN - это микроархитектура RISC SIMD (точнее SIMT ), контрастирующая с VLIW SIMD архитектура TeraScale. GCN требует значительно больше транзисторов, чем TeraScale, но дает преимущества для вычислений GPGPU. Это упрощает компилятор и должно также привести к лучшему использованию.

Графические чипы GCN изготавливаются с CMOS на 28 нм и с FinFET на 14 нм (от Samsung Electronics и GlobalFoundries ) и 7 нм (от TSMC ), доступный на некоторых моделях в Radeon HD 7000, HD 8000, 200, 300, 400 Графические карты AMD Radeon серии, 500 и Vega, включая отдельно выпущенную Radeon VII. GCN также используется в графической части AMD Accelerated Processing Units (APU), например, в APU PlayStation 4 и Xbox One.

Набор команд GCN принадлежит AMD (которой также принадлежит набор команд X86-64 ). Набор команд GCN был разработан специально для графических процессоров (и GPGPU) и, например, не имеет микрооперации для деления.

. Доступна документация для:

Для набора инструкций GCN доступен генератор кода LLVM (серверная часть компилятора). Он используется Mesa 3D.

GNU Compiler Collection (GCC) поддерживает GCN 3 (Fiji, Carrizo) и GCN 5 (Vega) с 2019 года (GCC 9) для однопоточных автономных программ, а с GCC 10 также выполняется разгрузка через OpenMP и OpenACC.

MIAOW - это RTL-реализация с открытым исходным кодом. e Набор инструкций GPGPU AMD Южных островов (он же Graphics Core Next).

В ноябре 2015 года AMD объявила о «Больцмановской инициативе». Инициатива AMD Boltzmann позволит переносить приложения на основе CUDA на общую модель программирования C ++.

На выставке «Super Computing 15» AMD продемонстрировала свои гетерогенные вычисления Компилятор (HCC), автономный драйвер Linux и HSA инфраструктура времени выполнения для кластерного класса, инструмент высокопроизводительных вычислений (HPC) и интерфейс гетерогенных вычислений для переносимости (HIP) для переноса приложений на основе CUDA на общая модель программирования C ++.

По состоянию на июль 2017 года семейство микроархитектур, реализующее идентично названный набор команд «Graphics Core Next», претерпело пять итераций. Различия в наборе инструкций минимальны и не слишком отличаются друг от друга. Исключением является архитектура GCN пятого поколения, которая сильно модифицировала потоковые процессоры для повышения производительности и поддержки одновременной обработки двух чисел с более низкой точностью вместо одного числа с более высокой точностью.

команда GCN обработка: каждый асинхронный вычислительный модуль (ACE) может анализировать входящие команды и отправлять работу вычислительным модулям (CU). Каждый ACE может управлять до 8 независимыми очередями. ACE могут работать параллельно с графическим командным процессором и двумя механизмами DMA. Процессор графических команд обрабатывает очереди графики, ACE обрабатывает очереди вычислений, а механизмы DMA обрабатывают очереди копирования. Каждая очередь может отправлять рабочие элементы, не дожидаясь завершения других задач, что позволяет чередовать независимые потоки команд в шейдере графического процессора

команда GCN обработка: каждый асинхронный вычислительный модуль (ACE) может анализировать входящие команды и отправлять работу вычислительным модулям (CU). Каждый ACE может управлять до 8 независимыми очередями. ACE могут работать параллельно с графическим командным процессором и двумя механизмами DMA. Процессор графических команд обрабатывает очереди графики, ACE обрабатывает очереди вычислений, а механизмы DMA обрабатывают очереди копирования. Каждая очередь может отправлять рабочие элементы, не дожидаясь завершения других задач, что позволяет чередовать независимые потоки команд в шейдере графического процессора «Графический командный процессор» (GCP) является функциональным блоком. микроархитектуры GCN. Помимо прочего, он отвечает за асинхронные шейдеры. В коротком видео Асинхронные шейдеры AMD показаны различия между «многопоточностью», «вытеснением » и «асинхронными шейдерами ».

Асинхронная вычислительная машина (ACE) - это отдельный функциональный блок, служащий вычислительным целям. Его назначение аналогично назначению графического командного процессора.

Начиная с третьей итерации GCN, оборудование содержит два планировщика: один для планирования волновых фронтов во время выполнения шейдера (планировщик CU, см. ниже) и новый для планирования выполнения очередей рисования и вычислений. Последнее способствует повышению производительности за счет выполнения вычислительных операций, когда CU недостаточно используются из-за того, что графические команды ограничены фиксированной скоростью конвейера функций или полосой пропускания. Эта функция известна как асинхронное вычисление.

Для данного шейдера драйверы графического процессора также должны выбрать правильный порядок инструкций, чтобы минимизировать задержку. Это делается на центральном процессоре и иногда называется «планирование».

Геометрический процессор

Геометрический процессор Геометрический процессор содержит ассемблер геометрии, тесселлер и вершинный ассемблер.

GCN Tesselator процессора Geometry может выполнять тесселяцию аппаратно, как определено Direct3D 11 и OpenGL 4.5 (см. AMD 21 января 2017 г.).

GCN Tesselator - это самый последний блок SIP AMD, более ранние блоки были ATI TruForm и аппаратной тесселяцией в TeraScale.

Один вычислительный блок объединяет 64 шейдера процессоры с 4 TMU. Вычислительный блок отделен от блоков вывода рендеринга (ROP), но подается в них. Каждый вычислительный модуль состоит из CU Scheduler, Branch Message Unit, 4 векторных модуля SIMD (каждый шириной 16 полос), 4 файлов VGPR по 64 КБ, 1 скалярного модуля, файла GPR 4 КБ, локального общего ресурса данных размером 64 КБ 4 блока текстурных фильтров, 16 блоков загрузки / сохранения текстурных выборок и кэш L1 объемом 16 КиБ. Четыре вычислительных блока подключены для совместного использования кэша инструкций размером 16 КиБ и кэша скалярных данных размером 32 КБайт. Они поддерживаются кешем L2. SIMD-VU работает с 16 элементами одновременно (за цикл), а SU может работать с одним элементом за раз (один за цикл). Кроме того, SU выполняет некоторые другие операции, такие как ветвление.

Каждый SIMD-VU имеет некоторую частную память, в которой он хранит свои регистры. Есть два типа регистров: скалярные регистры (s0, s1 и т. Д.), Каждый из которых содержит 4 байта, и векторные регистры (v0, v1 и т. Д.), Которые представляют собой набор из 64 4-х байтовых номеров каждый. Когда вы работаете с векторными регистрами, каждая операция выполняется параллельно с 64 числами. Каждый раз, когда вы работаете с ними, вы фактически работаете с 64 входами. Например, вы работаете с 64 разными пикселями одновременно (для каждого из них входы немного отличаются, и поэтому вы получаете немного другой цвет в конце).

В каждом SIMD-VU есть место для 512 скалярных регистров и 256 векторных регистров.

Планировщик CU - это аппаратный функциональный блок, выбирающий для SIMD-VU, какие волновые фронты выполнять. Для планирования он выбирает один SIMD-VU на цикл. Не следует путать с другими планировщиками аппаратного или программного обеспечения.

Во всех GCN-GPU «волновой фронт» состоит из 64 потоков, а во всех графических процессорах Nvidia «warp» состоит из 32 потоков.

Решение AMD состоит в том, чтобы назначить несколько волновых фронтов каждому SIMD-VU. Аппаратное обеспечение распределяет регистры по разным волновым фронтам, и когда один волновой фронт ожидает некоторого результата, который находится в памяти, планировщик CU решает заставить SIMD-VU работать на другом волновом фронте. Волновые фронты привязаны к SIMD-VU. SIMD-VU не обмениваются волновыми фронтами. Максимум 10 волновых фронтов можно отнести к SIMD-VU (таким образом, 40 на CU).

AMD CodeXL показывает таблицы с отношениями между количеством SGPR и VGPR к количеству волновых фронтов, но в основном для SGPRS это min (104, 512 / количество волновых фронтов) и VGPRS 256 / количество волновых фронтов.

Обратите внимание, что в сочетании с инструкциями SSE эту концепцию базового уровня параллелизма часто называют «шириной вектора». Ширина вектора характеризуется общим количеством битов в нем.

Каждый векторный блок SIMD имеет:

Каждый SIMD-VU имеет 10 буферов инструкций волнового фронта, и для его выполнения требуется 4 цикла один волновой фронт.

Многие реализации GCN обычно сопровождаются несколькими другими блоками AMD ASIC. Включая, помимо прочего, Unified Video Decoder, Video Coding Engine и AMD TrueAudio.

В превью в 2011 году AnandTech писал об объединенной виртуальной памяти, поддерживаемой Graphics Core Next.

Архитектура классического настольного компьютера с четкой графикой карта поверх PCI Express. CPU и GPU имеют отдельную физическую память с разными адресными пространствами. Все данные необходимо скопировать по шине PCIe. Примечание: на диаграмме показана пропускная способность, но не задержка памяти..

GCN поддерживает «унифицированную виртуальную память», поэтому позволяет нулевое копирование вместо данных, только указатели скопированы, "пропущены". Это первостепенная функция HSA.

Интегрированные графические решения (и APU AMD с графикой TeraScale ) страдают от разделения основной памяти: часть системной памяти выделяется исключительно графическому процессору. Нулевое копирование невозможно, данные необходимо копировать (по шине системной памяти) из одного раздела в другой.

APU AMD с графикой GCN выигрывают от единой основной памяти, сохраняя ограниченную полосу пропускания.

GCN включает специальные функциональные блоки, которые будут использоваться HSA. Поддержка этих функциональных блоков доступна через amdkfd, начиная с ядра Linux 3.19.

GCN включает специальные функциональные блоки, которые будут использоваться HSA. Поддержка этих функциональных блоков доступна через amdkfd, начиная с ядра Linux 3.19. Некоторые из конкретных функций HSA, реализованных в оборудовании, нуждаются в поддержке со стороны ядра операционной системы (его подсистем) и / или из конкретных драйверов устройств. Например, в июле 2014 года AMD опубликовала набор из 83 патчей, которые будут объединены в основную линию ядра Linux 3.17 для поддержки видеокарт Radeon на базе Graphics Core Next. Специальный драйвер под названием «Драйвер ядра HSA» находится в каталоге / drivers / gpu / hsa, а драйверы графических устройств DRM - в / drivers / gpu / drm и дополняет уже существующие существующий драйвер DRM для карт Radeon. Эта самая первая реализация фокусируется на одном APU "Kaveri" и работает вместе с существующим графическим драйвером ядра Radeon (kgd).

Они используются для выполнения планирования и разгрузки назначения очередей вычислений элементам управления доступом от драйвера к оборудованию путем буферизации этих очередей до тех пор, пока есть по крайней мере одна пустая очередь по крайней мере в одном ACE, в результате чего HWS немедленно назначает буферизованные очереди ACE, пока все очереди не будут заполнены или не останется очередей для безопасного назначения. Часть выполняемой работы по планированию включает в себя очереди с приоритетами, которые позволяют критическим задачам выполняться с более высоким приоритетом, чем другие задачи, без необходимости вытеснения задач с более низким приоритетом для выполнения задачи с высоким приоритетом, что позволяет задачам выполняться одновременно с задачами с высоким приоритетом запланировано, чтобы максимально использовать графический процессор, позволяя другим задачам использовать ресурсы, которые не используются задачами с высоким приоритетом. По сути, это асинхронные вычислительные машины, в которых отсутствуют диспетчерские контроллеры. Впервые они были представлены в микроархитектуре GCN четвертого поколения, но присутствовали в микроархитектуре GCN третьего поколения для целей внутреннего тестирования. Обновление драйвера позволило использовать аппаратные планировщики в частях GCN третьего поколения для производственного использования.

Этот модуль отбрасывает вырожденные треугольники перед тем, как они войдут в вершинный шейдер и треугольники, которые не закрывают никакие фрагменты до того, как войдут в шейдер фрагментов. Этот блок был представлен с микроархитектурой GCN четвертого поколения.

| Дата выпуска | январь 2012 г.; 8 лет назад (январь 2012 г.) |

|---|---|

| История | |

| Предшественник | TeraScale 3 |

| Преемник | Graphics Core Next 2 |

Существуют асинхронные вычислительные машины, управляющие вычислениями и диспетчеризацией.

ZeroCore Power - это долгая технология энергосбережения в режиме ожидания, отключение функциональных блоков графического процессора, когда он не используется. Технология AMD ZeroCore Power дополняет AMD PowerTune.

дискретные графические процессоры (семейство Southern Islands):

| Дата выпуска | сентябрь 2013 г.; 7 лет назад (сентябрь 2013 г.) |

|---|---|

| История | |

| Предшественник | Графическое ядро Next 1 |

| Преемник | Графическое ядро Next 3 |

AMD PowerTune «Bonaire»

AMD PowerTune «Bonaire» GCN 2-го поколения был представлен с Radeon HD 7790 и также встречается в Radeon HD 8770, R7 260 / 260X, R9 290 / 290X, R9 295X2, R7 360, R9 390 / 390X, а также Steamroller -based Desktop Kaveri APU и Mobile Kaveri APU и в Puma на базе APU "Beema" и "Mullins". Он имеет множество преимуществ по сравнению с исходной GCN, включая поддержку FreeSync, AMD TrueAudio и обновленную версию технологии AMD PowerTune.

GCN 2-го поколения представило объект под названием «Shader Engine» (SE). Шейдерный движок включает один геометрический процессор, до 44 CU (чип Hawaii), растеризаторы, ROP и кэш L1. В состав Shader Engine не входят графический командный процессор, 8 элементов управления доступом, контроллеры кэша L2 и памяти, а также ускорители аудио и видео, контроллеры дисплея, 2 контроллера DMA и Интерфейс PCIe.

A10-7850K "Kaveri" содержит 8 CU (вычислительные блоки) и 8 асинхронных вычислительных модулей для независимого планирования и диспетчеризации рабочих элементов.

На AMD Developer Summit ( APU) в ноябре 2013 Майкл Мантор представил Radeon R9 290X.

дискретные графические процессоры (семейство Sea Islands):

интегрировано в APU:

| Дата выпуска | июнь 2015 г.; 5 лет назад (июнь 2015 г.) |

|---|---|

| История | |

| Предшественник | Графическое ядро Next 2 |

| Преемник | Графическое ядро Next 4 |

GCN 3-го поколения было представлено в 2014 году с Radeon R9 285 и R9 M295X с графическим процессором Tonga. Он отличается улучшенной производительностью тесселяции, сжатием дельта-цвета без потерь для уменьшения использования полосы пропускания памяти, обновленным и более эффективным набором инструкций, новым высококачественным скейлером для видео и новым мультимедийным движком (видеокодер / декодер). В Mesa поддерживается сжатие дельта-цветов. Однако его производительность с двойной точностью хуже по сравнению с предыдущим поколением.

дискретные графические процессоры:

, интегрированной в APU:

| Дата выпуска | июнь 2016 г.; 4 года назад (июнь 2016 г.) |

|---|---|

| История | |

| Предшественник | Графическое ядро Next 3 |

| Преемник | Графическое ядро Next 5 |

GPU семейства Arctic Islands были представлены во втором квартале 2016 года с AMD Radeon 400 серии. 3D-движок (например, GCA (Graphics and Compute array) или GFX) идентичен таковому в чипах Tonga. Но Polaris имеет новый движок Display Controller, UVD версии 6.3 и т. Д.

Все чипы на базе Polaris, кроме Polaris 30, производятся на 14-нм FinFET процесс, разработанный Samsung Electronics и лицензированный GlobalFoundries. Немного более новый обновленный Polaris 30 построен на технологическом узле 12 нм LP FinFET, разработанном Samsung и GlobalFoundries. Архитектура набора команд GCN четвертого поколения совместима с третьим поколением. Это оптимизация для 14-нм процесса FinFET, обеспечивающая более высокие тактовые частоты графического процессора, чем у третьего поколения GCN. Архитектурные улучшения включают новые аппаратные планировщики, новый примитивный ускоритель отбрасывания, новый контроллер дисплея и обновленный UVD, который может декодировать HEVC с разрешением 4K со скоростью 60 кадров в секунду с 10 битами на канал цвета.

дискретные графические процессоры:

Производительность FP64 всех графических процессоров GCN 4-го поколения составляет / 16 производительности FP32.

| Дата выпуска | июнь 2017 г.; 3 года назад (июнь 2017 г.) |

|---|---|

| История | |

| Предшественник | Графическое ядро Next 4 |

| Преемник | RDNA 1 |

AMD начала раскрывать подробности своего следующего поколения архитектуры GCN, получившего название «Next -Generation Compute Unit ', январь 2017 г. Ожидалось, что новый дизайн увеличит инструкций на такт, более высокие тактовые частоты, поддержку HBM2, больший объем памяти адресное пространство. Наборы микросхем дискретной графики также включают «HBCC (High Bandwidth Cache Controller)», но не при интеграции в APU. Кроме того, ожидается, что новые микросхемы будут включать улучшения в модулях Растеризация и Рендеринг. Потоковые процессоры сильно модифицированы по сравнению с предыдущими поколениями, чтобы поддерживать упакованную математическую технологию Rapid Pack Math для 8-битных, 16-битных и 32-битных чисел. Это дает существенное преимущество в производительности, когда приемлема более низкая точность (например: обработка двух чисел половинной точности с той же скоростью, что и одного числа одинарной точности ).

Nvidia представила растеризацию и биннинг на основе тайлов с помощью Maxwell, и это стало большой причиной повышения эффективности Maxwell. В январе AnandTech предположил, что Vega наконец догонит Nvidia в отношении оптимизации энергоэффективности благодаря новому «DSBR (Draw Stream Binning Rasterizer)», который будет представлен вместе с Vega.

Он также добавлена поддержка нового этапа шейдера - Primitive Shaders. Примитивные шейдеры обеспечивают более гибкую обработку геометрии и заменяют вершинные и геометрические шейдеры в конвейере рендеринга. По состоянию на декабрь 2018 года примитивные шейдеры нельзя использовать, поскольку необходимые изменения API еще не внесены.

Vega 10 и Vega 12 используют 14 нм FinFET, разработанный Samsung Electronics и лицензированный GlobalFoundries. Vega 20 использует процесс 7 нм FinFET, разработанный TSMC.

дискретные графические процессоры:

интегрированы в APU:

Двойная точность с плавающей запятой (FP64) производительность всех графических процессоров GCN 5-го поколения, кроме Vega 20, составляет / 16 производительности FP32. Для Vega 20 это / 2 производительности FP32. Все графические процессоры GCN 5-го поколения поддерживают вычисления с плавающей запятой половинной точности (FP16), что вдвое превышает производительность FP32.